ۉᇸ࠶ኸళ

ڤዝᅏഗ

3Q 2008

5

ۆ႙ۉᇸᆌᆩ

تഗۉᇸݛӄ

ڤዝᅏഗڦۉᇸ࠶ׂྺڦ

DSP

ǃ

FPGA

ඪᅪഄتഗ༵ࠃፌᆫࣅڦࠃۉ

DŽ

ஃظڦۉࠃۉڦยԢ࣏ߛࠀ୲ڦ

၍በ

ˈ

ۼీቴڟፁُૌᆌᆩዐڦتഗڦჹႴ൱ڦۉᇸݛӄ

DŽ

ᅜူຕᄻڦยݛܔณຕُૌݛӄႜକዘۅຫ

DŽ

www.ti.com.cn/processorpower

ߛࠀၳবู

(Space-Efficient)

ڦ

DM355

֖ย

2.0 V to 5.5 V

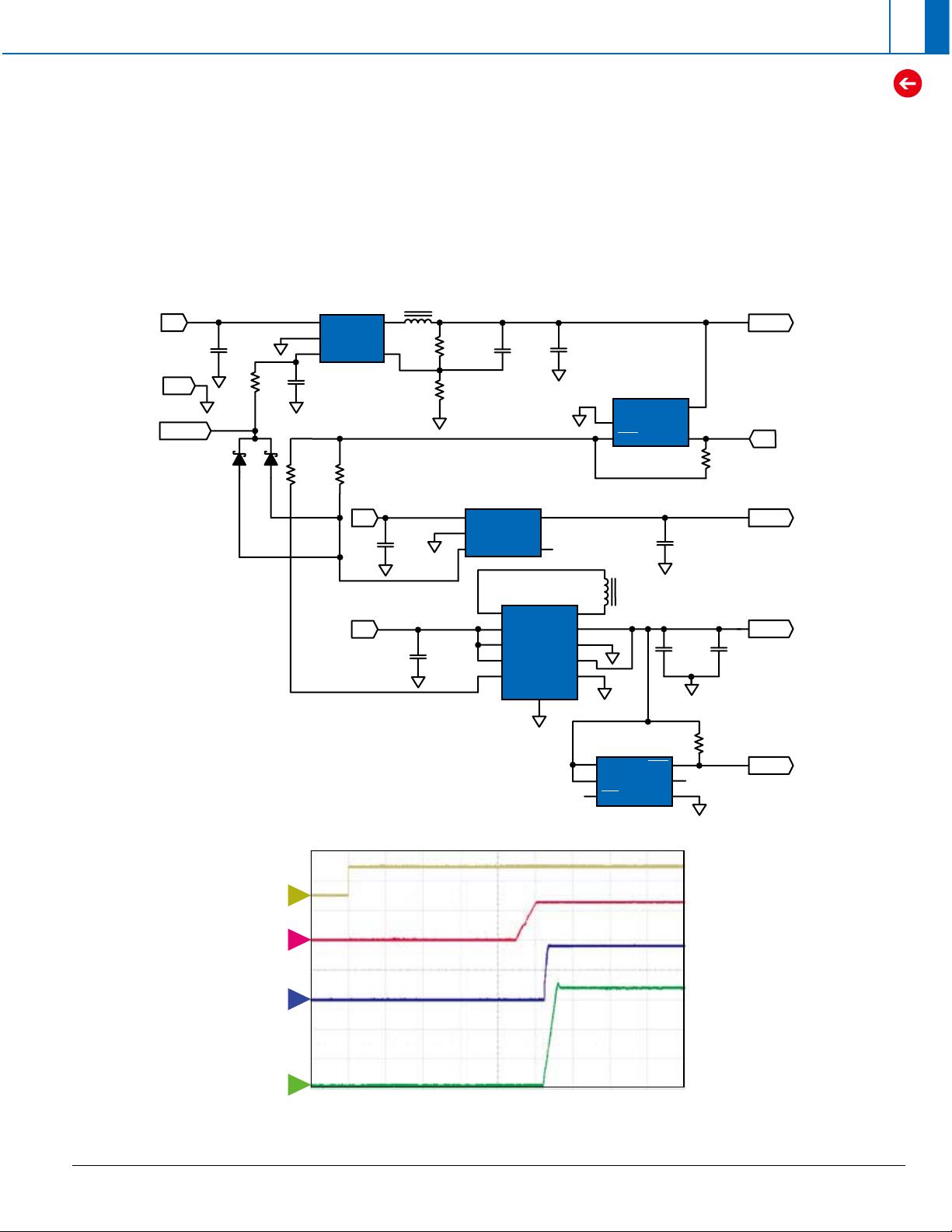

U1

TPS62240DDC

U2

TPS3803-01DCK

U3

TPS72118DBV

VIN

VOUT1

VOUT2

VOUT3

/RESET

20-ms Delay

11

VIN

VIN

5-μs Delay

1.3 V, 210 mA

1.8 V, 30 mA

3.3 V, 95 mA

15

L1

2.2 μH

L2

2.2 μH

2

3

GND

ENABLE

C1

10 μF

C2

10 μF

C3

33

pF

C4

10 μF

C5

10 μF

C6

10 μF

C8

10 μF

C9

10 μF

D1

BAT54C

R1

5k

R2

36

5k

R3

316

k

R4

50 k

R7

10

0k

R5

200

k

R6

200

k

15

2

34

15

2

3

4

U4

TPS63001DRC

VIN

C7

10 μF

4

5

8

7

6

2

1

3

10

9

U5

TPS3808G33DBV

6

5

3

1

4

2

SW

FB

VI

GND

EN

SNS/NC

VDD

NC

GND

RST

OUT

NR/FB

IN

GND

EN

PwPd

L1

VIN

VINA

Sync/PS

EN

L2

VOUT

PGND

FB

GND

VDD

SNS

MR

RST

CT

GND

4

C4

C3

C2

C1

Enable (2 V/div)

V = 1.3 V (1 V/div)

OUT

V = 1.8 V (1 V/div)

OUT

V = 3.3 V (1 V/div)

OUT

Timebase = 500 μs/div

ۆ႙ഔۯհႚ

评论1

最新资源