没有合适的资源?快使用搜索试试~ 我知道了~

基于单片机控制的交通灯

需积分: 0 1 下载量 56 浏览量

2013-12-06

16:21:11

上传

评论

收藏 2.03MB DOC 举报

温馨提示

试读

17页

基于单片机控制的交通灯,好好爱好爱好爱好特别好,做过路过不要错过

资源推荐

资源详情

资源评论

基于单片机控制的 LED 交通灯

前言

十字路口车辆穿梭,行人熙攘,车行车道,人行人道,有条不紊。那么靠

什么来实现这井然秩序呢?靠的是交通信号灯的自动指挥系统。交通灯控制系

统虽然常见平凡,但其现实意义、经济效益重大。合理有效的交通灯控制系统

能有效的减少“塞车”等交通问题,减少交警的工作压力,保证行客安全。

交通信号灯控制方式很多。传统的交通灯控制电路一般由数字电路构成,

电路复杂、体积大、成本高,而且不利于管理与调配。采用单片机控制交通灯

不但可以解决上述问题,而且还具有实时调节功能、时间显示功能、语音提示

功能等,非常方便。

LED 交通信号灯与传统的白炽灯相比,其优点有:1、工作寿命长,一般

可以达到 10 年,如果考虑恶劣环境,预计寿命也可达到 5~6 年。LED 灯的更

换成本大大低于白炽灯。2、能耗低,一个直径为 30cm(12 英寸)的白炽交

通信号灯的耗电量为 150W,横过马路人行道的交通警示灯的耗电量为 67W,

而 LED 交通信号灯的耗电量仅为 15W。3、作为一种“第四代”绿色光源,必然

是未来发展的趋势。国家也将从绿色、环保、节能等方面考虑而鼓励该行业的

发展。照明方向将是 LED 未来的发展方向,预计未来 LED 的价格将大大降低,

该系统利用 LED 作为照明光源,具有一定的创新性和科学性。

但是,在国内外,由于交通信号灯控制系统历史悠久,人们往往对其忽视 。

像实时控制、语音提示等问题尚无引起人们重视。而这些功能的应用与人们的

利益切切相关。本团队正是针对这些问题,构造出一个合理有效的交通灯控制

系统,一旦投入应用,将对社会产生巨大的影响,其经济效益明显。

单片机概述

单片机微型计算机是微型计算机的一个重要分支,也是颇具生命力的机种。

单片机微型计算机简称单片机,特别适用于控制领域,故又称为微控制器。

通常,单片机由单块集成电路芯片构成,内部包含有计算机的基本功能部

件:中央处理器、存储器和 I/O 接口电路等。因此,单片机只需要和适当的软

件 及 外 部 设 备 相 结 合 , 便 可 成 为 一 个 单 片 机 控 制 系 统 。 单 片 机 经 过

1、2、3、3 代的发展,目前单片机正朝着高性能和多品种方向发展,它们的

CPU 功能在增强,内部资源在增多,引角的多功能化,以及低电压底功耗。

芯片简介

AT89S51 是一个低功耗,高性能 CMOS 8 位单片机,片内含 4k Bytes

ISP(In-system programmable)的可反复擦写 1000 次的 Flash 只读程序存

储器,器件采用 ATMEL 公司的高密度、非易失性存储技术制造,兼容标准

MCS-51 指令系统及 80C51 引脚结构,芯片内集成了通用 8 位中央处理器和

ISP Flash 存储单元,功能强大的微型计算机的 AT89S51 可为许多嵌入式控制

应用系统提供高性价比的解决方案。

AT89S51 具有如下特点:40 个引脚,4k Bytes Flash 片内程序存储器,

128 bytes 的随机存 取数据存储器 ( RAM), 32 个外部双 向输入/输出

(I/O)口,5 个中断优先级 2 层中断嵌套中断,2 个 16 位可编程定时计数

器,2 个全双工串行通信口,看门狗(WDT)电路,片内时钟振荡器。

此外,AT89S51 设计和配置了振荡频率可为 0Hz 并可通过软件设置省电

模式。空闲模式下,CPU 暂停工作,而 RAM 定时计数器,串行口,外中断系

统可继续工作,掉电模式冻结振荡器而保存 RAM 的数据,停止芯片其它功能直

至外中断激活或硬件复位。同时该芯片还具有 PDIP、TQFP 和 PLCC 等三种封

装形式,以适应不同产品的需求。

AT89S51 具有如下特点:40 个引脚,4k Bytes Flash 片内程序存储器,

128 bytes 的随机存 取数据存储器 ( RAM), 32 个外部双 向输入/输出

(I/O)口,5 个中断优先级 2 层中断嵌套中断,2 个 16 位可编程定时计数

器,2 个全双工串行通信口,看门狗(WDT)电路,片内时钟振荡器。 此外,

AT89S51 设计和配置了振荡频率可为 0Hz 并可通过软件设置省电模式。空闲

模式下,CPU 暂停工作,而 RAM 定时计数器,串行口,外中断系统可继续工

作,掉电模式冻结振荡器而保存 RAM 的数据,停止芯片其它功能直至外中断激

活或硬件复位。同时该芯片还具有 PDIP、TQFP 和 PLCC 等三种封装形式,以

适应不同产品的需求。

1.主要特性:

• 8031 CPU 与 MCS-51 兼容

• 4K 字节可编程 FLASH 存储器(寿命:1000 写/擦循环)

• 全静态工作:0Hz-24KHz

• 三级程序存储器保密锁定

• 128*8 位内部 RAM

• 32 条可编程 I/O 线

• 两个 16 位定时器/计数器

• 6 个中断源

• 可编程串行通道

• 低功耗的闲置和掉电模式

• 片内振荡器和时钟电路

2.管脚说明:

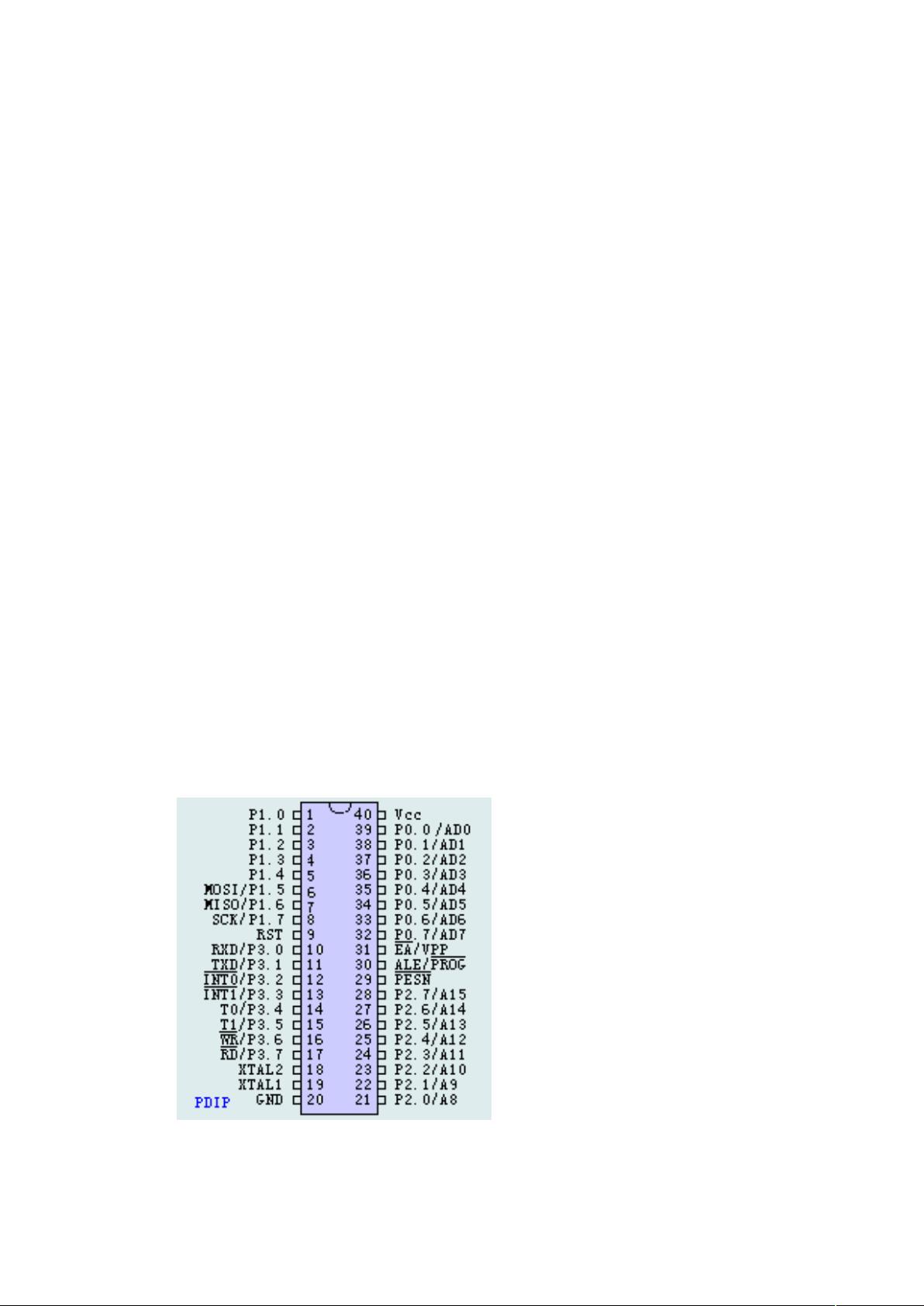

图 1 AT89S51 引脚图

VCC:供电电压。

GND:接地。

P0 口:P0 口为一个 8 位漏级开路双向 I/O 口,每脚可吸收 8TTL 门电流。

当 P1 口的管脚第一次写 1 时,被定义为高阻输入。P0 能够用于外部程序数据

存储器,它可以被定义为数据/地址的第八位。在 FIASH 编程时,P0 口作为原

码输入口,当 FIASH 进行校验时,P0 输出原码,此时 P0 外部必须被拉高。

P1 口:P1 口是一个内部提供上拉电阻的 8 位双向 I/O 口,P1 口缓冲器能

接收输出 4TTL 门电流。P1 口管脚写入 1 后,被内部上拉为高,可用作输入,

P1 口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在

FLASH 编程和校验时,P1 口作为第八位地址接收。

P2 口:P2 口为一个内部上拉电阻的 8 位双向 I/O 口,P2 口缓冲器可接收,

输出 4 个 TTL 门电流,当 P2 口被写“1”时,其管脚被内部上拉电阻拉高,且作

为输入。并因此作为输入时,P2 口的管脚被外部拉低,将输出电流。这是由于

内部上拉的缘故。P2 口当用于外部程序存储器或 16 位地址外部数据存储器进

行存取时,P2 口输出地址的高八位。在给出地址“1”时,它利用内部上拉优势,

当对外部八位地址数据存储器进行读写时,P2 口输出其特殊功能寄存器的内容。

P2 口在 FLASH 编程和校验时接收高八位地址信号和控制信号。

P3 口:P3 口管脚是 8 个带内部上拉电阻的双向 I/O 口,可接收输出 4 个

TTL 门电流。当 P3 口写入“1”后,它们被内部上拉为高电平,并用作输入。作

为输入,由于外部下拉为低电平,P3 口将输出电流(ILL)这是由于上拉的缘

故。

P3.0 RXD(串行输入口)

P3.1 TXD(串行输出口)

P3.2 /INT0(外部中断 0)

P3.3 /INT1(外部中断 1)

P3.4 T0(记时器 0 外部输入)

P3.5 T1(记时器 1 外部输入)

P3.6 /WR(外部数据存储器写选通)

P3.7 /RD(外部数据存储器读选通)

P3 口同时为闪烁编程和编程校验接收一些控制信号。

I/O 口作为输入口时有两种工作方式即所谓的读端口与读引脚读端口时实际

上并不从外部读入数据而是把端口锁存器的内容读入到内部总线经过某种运算

或变换后再写回到端口锁存器只有读端口时才真正地把外部的数据读入到内部

总线上面图中的两个三角形表示的就是输入缓冲器 CPU 将根据不同的指令分别

发出读端口或读引脚信号以完成不同的操作这是由硬件自动完成的不需要我们

操心 1 然后再实行读引脚操作否则就可能读入出错为什么看上面的图如果不对

端口置 1 端口锁存器原来的状态有可能为 0Q 端为 0Q^为 1 加到场效应管栅极

的信号为 1 该场效应管就导通对地呈现低阻抗,此时即使引脚上输入的信号为 1

也会因端口的低阻抗而使信号变低使得外加的 1 信号读入后不一定是 1 若先执

行置 1 操作则可以使场效应管截止引脚信号直接加到三态缓冲器中实现正确的

读入由于在输入操作时还必须附加一个准备动作所以这类 I/O 口被称为准双向

口 89C51 的 P0/P1/P2/P3 口作为输入时都是准双向口接下来让我们再看另一

个问题从图中可以看出这四个端口还有一个差别除了 P1 口外 P0P2P3 口都还

有其他的功能

RST:复位输入。当振荡器复位器件时,要保持 RST 脚两个机器周期的高

剩余16页未读,继续阅读

资源评论

giraffeee

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功