没有合适的资源?快使用搜索试试~ 我知道了~

Xilinx FPGA DDR4 接口应用分析

温馨提示

试读

26页

该文件是FPGA中运用DDR4的接口应用解析,分析了FPGA和DDR4之间的连接

资源推荐

资源详情

资源评论

High Performance DDR4 interfaces with

FPGA Flexibility

Adrian Cosoroaba and Terry Magee

Xilinx, Inc.

© Copyright 2014 Xilinx

.

System Requirements for FPGA based systems

– Higher Bandwidth, Increased Flexibility, Lower Power

UltraScale FPGA Solution for DDR4 and other parallel

memory interfaces

PHY Solution for higher performance with maximum

flexibility

Multiple Solutions for Different Needs

AGENDA

© Copyright 2014 Xilinx

.

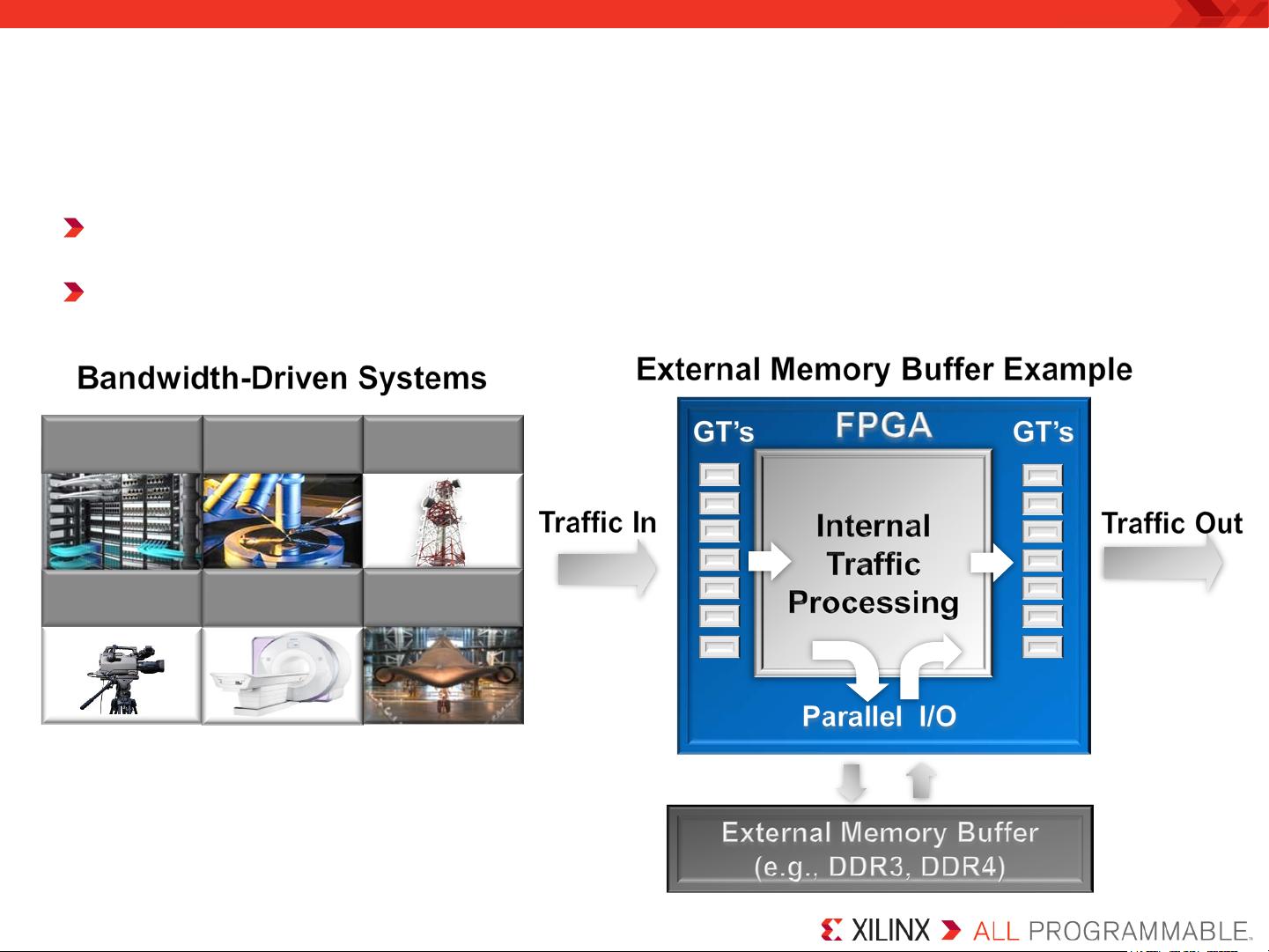

Rapid growth in serial I/O bandwidth is enabling next generation systems

External memory buffering rate must match or exceed traffic rate

Page 3

Bandwidth Driven Systems Demand Extensive

Memory Buffering

8x8 Multi-

Mode Radio

Semiconductor

ATE

Super Hi-

Vision Camera

Radar

Processing

Medical

Imaging

100G/200G

Networking

© Copyright 2014 Xilinx

.

Data rate per bit

Number of Interfaces (improves with better usage of I/O)

Data bus width

Data bus efficiency (percentage of time that data bus is utilized)

Page 4

FPGA Memory Interface Bandwidth

© Copyright 2014 Xilinx

.

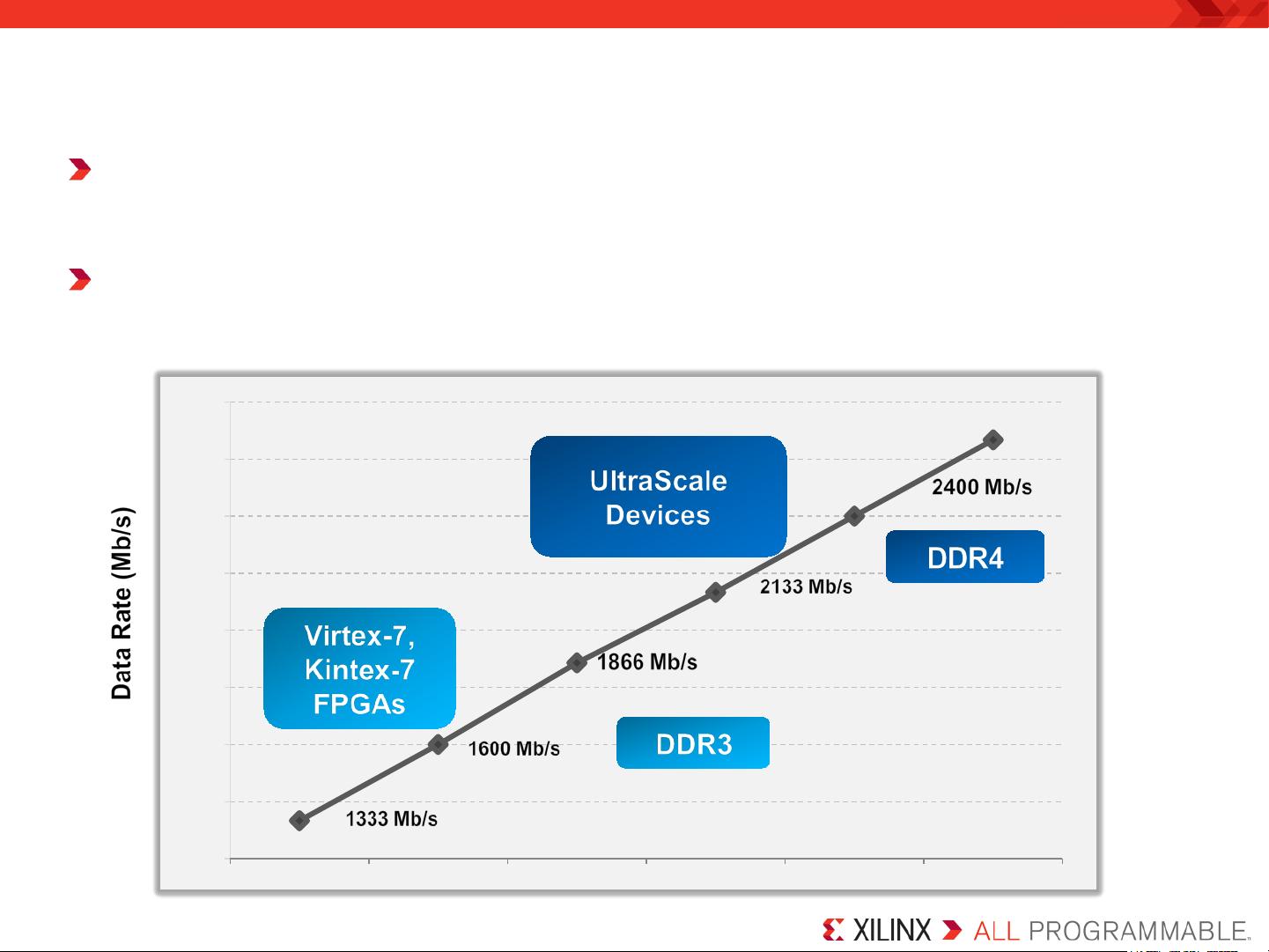

30% higher data rates vs. DDR3

– 2400 Mb/s (UltraScale devices) vs. 1866 Mb/s (7 series devices)

Available in both mid- and high-speed grade

– Lower cost benefits of a flexible architecture

Higher DDR4 Data Rates

1200

1400

1600

1800

2000

2200

2400

2600

2800

2010

2011

2012

2013

2014

2015

剩余25页未读,继续阅读

资源评论

Captain_船长2018-09-18纯粹是骗人的

Captain_船长2018-09-18纯粹是骗人的 九章子2018-03-24不要下载,骗人的,这是网络上的一篇文档,讲解的是ddr3与ddr4在io设计上不同之处

九章子2018-03-24不要下载,骗人的,这是网络上的一篇文档,讲解的是ddr3与ddr4在io设计上不同之处

共续天涯水

- 粉丝: 2

- 资源: 8

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功