Copyright © 2004 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device des-

ignations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and

service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Al-

tera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants

performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the ap-

plication or use of any information, product, or service described herein except as expressly agreed to in writing by Altera

Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published in-

formation and before placing orders for products or services.

ii DSP Builder Version 2.2.0 Altera Corporation

DSP Builder User Guide Preliminary August 2004

UG-DSPBUILDER-1.1

Altera Corporation DSP Builder Version 2.2.0 iii

August 2004

Contents

About This User Guide

Revision History ..................................................................................................................................... vii

How to Contact Altera ...................................................................................................................... 1–viii

Typographic Conventions .................................................................................................................... viii

Chapter 1. About DSP Builder

New Features in Version 2.2.0 ............................................................................................................. 1–1

Features ................................................................................................................................................... 1–1

General Description ............................................................................................................................... 1–2

High-Speed DSP with Programmable Logic ................................................................................ 1–2

Chapter 2. Getting Started

DSP Builder Software Requirements .................................................................................................. 2–1

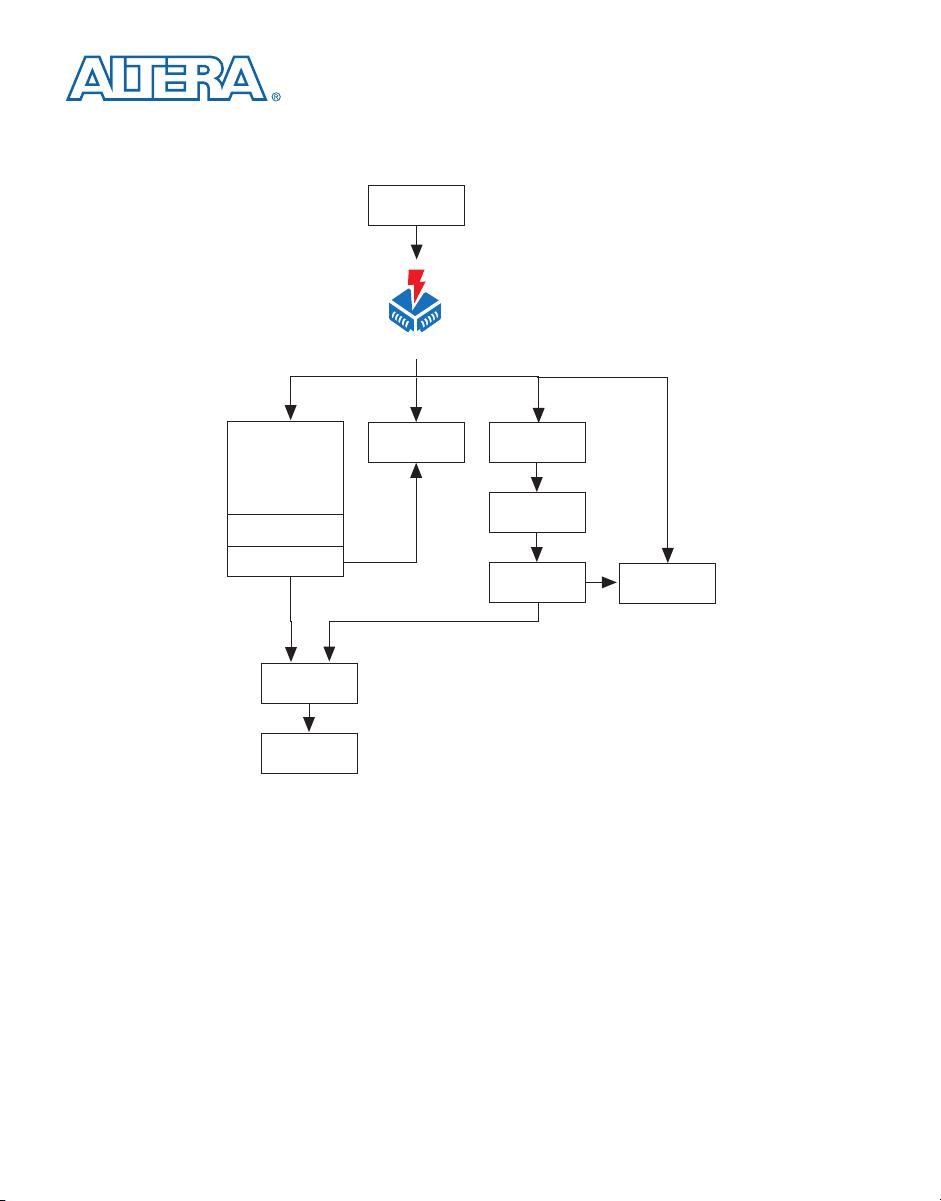

Design Flow ............................................................................................................................................ 2–1

Install DSP Builder ................................................................................................................................ 2–3

Obtaining DSP Builder .................................................................................................................... 2–3

Installing DSP Builder ..................................................................................................................... 2–3

DSP Builder Directory Structure .................................................................................................... 2–5

Set Up Licensing .................................................................................................................................... 2–5

Appending the License to Your license.dat File .......................................................................... 2–6

Specify the License File Location Using LM_LICENSE_FILE ................................................... 2–7

Chapter 3. DSP Builder Tutorial

Introduction ............................................................................................................................................ 3–1

Creating the Amplitude Modulator Model ....................................................................................... 3–2

Create a New Model ........................................................................................................................ 3–4

Add the Sine Wave Block ................................................................................................................ 3–5

Add the SinIn Block ......................................................................................................................... 3–6

Add the Delay Block ........................................................................................................................ 3–8

Add the SinDelay Block .................................................................................................................. 3–9

Add the Mux Block ........................................................................................................................ 3–10

Add the Random Number Block ................................................................................................. 3–11

Add the Noise Block ...................................................................................................................... 3–12

Add the BusBuild Block ................................................................................................................ 3–13

Add the GND Block ....................................................................................................................... 3–14

Add the Product Block .................................................................................................................. 3–14

Add the StreamMod Block ............................................................................................................ 3–15

Add the Scope Block ...................................................................................................................... 3–16

Add the SignalCompiler Block ..................................................................................................... 3–17

Simulate Your Model in Simulink ............................................................................................... 3–18

iv DSP Builder Version 2.2.0 Altera Corporation

DSP Builder User Guide August 2004

Contents

Performing RTL Simulation ............................................................................................................... 3–20

Synthesizing & Compiling the Design ............................................................................................. 3–22

Automated Flow (Within Simulink) ............................................................................................ 3–23

Manual Flow (Outside Simulink) ................................................................................................ 3–23

Automated Synthesis & Compilation ......................................................................................... 3–24

Manual Synthesis & Compilation ................................................................................................ 3–25

Chapter 4. DSP Builder Design Rules

DSP Builder Naming Conventions ..................................................................................................... 4–1

Bit Width Design Rule .......................................................................................................................... 4–1

Fixed-Point Notation ............................................................................................................................. 4–2

Binary Point Location in Signed Binary Fractional Format ............................................................. 4–3

Frequency Design Rule ......................................................................................................................... 4–5

Single Clock Domain ....................................................................................................................... 4–5

Multiple Clock Domains ............................................................................................................... 4–10

Using Advanced PLL Features .....................................................................................................4–14

Timing Semantics Between Simulink and VHDL or Verilog HDL Simulation .......................... 4–15

Simulink Simulation Model .......................................................................................................... 4–15

HDL Simulation Models ............................................................................................................... 4–15

Startup and Initial Conditions ...................................................................................................... 4–16

Reference Timing Diagram ........................................................................................................... 4–16

Hierarchical Design ............................................................................................................................. 4–17

Goto & From Block Support ............................................................................................................... 4–18

SignalCompiler Design Rules ............................................................................................................ 4–19

Using DSP Builder Modules in External RTL Designs .................................................................. 4–19

Black Boxing ......................................................................................................................................... 4–21

Chapter 5. Using MegaCore Functions

Introduction ............................................................................................................................................ 5–1

Installing MegaCore Functions ............................................................................................................ 5–1

Using MegaCore Functions .................................................................................................................. 5–3

Placing the MegaCore Function in the Simulink Model ............................................................ 5–3

Parameterizing the MegaCore Function Variation ..................................................................... 5–3

Generating the MegaCore Function Variation ............................................................................. 5–3

Connecting the MegaCore Function Variation to the Rest of the Model ................................. 5–3

Simulation ......................................................................................................................................... 5–4

Simulink Files Associated with a MegaCore Function ............................................................... 5–4

Updating MegaCore Function Variation Blocks .......................................................................... 5–4

MegaCore Function Walkthrough—A Low-pass FIR Filter ........................................................... 5–5

Create a new Simulink Model ........................................................................................................ 5–5

Placing the MegaCore function in the Simulink Model ............................................................. 5–6

Parameterizing the MegaCore Function Variation ..................................................................... 5–8

Generating the MegaCore Function Variation ........................................................................... 5–10

Connecting your MegaCore Function Variation to the Rest of Your Design ........................ 5–12

Simulation ....................................................................................................................................... 5–16

Add the SignalCompiler Block ..................................................................................................... 5–18

Performing RTL Simulation ............................................................................................................... 5–20

Altera Corporation DSP Builder Version 2.2.0 v

August 2004 DSP Builder User Guide

Contents

Chapter 6. Performing SignalTap II Logic Analysis

Introduction ............................................................................................................................................ 6–1

Open the Walkthrough Example Design ...................................................................................... 6–2

Specify the Nodes to Analyze ......................................................................................................... 6–5

Turn On the SignalTap II Option in SignalCompiler .................................................................. 6–7

Generate VHDL, Synthesize, Compile & Download the Design to the DSP Board ............... 6–8

Specify Trigger Conditions ............................................................................................................. 6–8

Specify the Radix for the Bus Groups ........................................................................................... 6–9

Perform SignalTap II Analysis ..................................................................................................... 6–10

Chapter 7. Using the SOPC Ports Library

Avalon Ports Walkthrough .................................................................................................................. 7–1

Open the Walkthrough Example Design ...................................................................................... 7–2

Turn On the SOPC Option in SignalCompiler & Generate VHDL & PTF Files ..................... 7–3

Instantiating your Design as a Custom Peripheral to the Nios Embedded Processor in SOPC

Builder ................................................................................................................................................ 7–4

Custom Instruction Walkthrough ....................................................................................................... 7–6

Open the Walkthrough Example Design ...................................................................................... 7–7

Turn On the SOPC Option in SignalCompiler & Generate VHDL & PTF Files ..................... 7–7

Including your Design as a Custom Instruction to the Nios II Embedded Processor in SOPC

Builder ................................................................................................................................................ 7–9

Chapter 8. Using the State Machine Library

Introduction ............................................................................................................................................ 8–1

Design Flow ............................................................................................................................................ 8–3

Chapter 9. Using Black Boxes for Non-DSP Builder Subsystems

Introduction ............................................................................................................................................ 9–1

Using the Subsystem

Builder block .......................................................................................................................................... 9–3

Create a Library Model File with the SubsystemBuilder Block ................................................ 9–3

Build the HDL Subsystem Simulation Model .............................................................................. 9–7

Simulating Using the Subsystem Block ...................................................................................... 9–10

Perform RTL Simulation in the ModelSim Simulator ............................................................... 9–12

Using Non-DSP Builder Blocksets ............................................................................................... 9–14

Chapter 10. Creating Custom Library Blocks

Overview .............................................................................................................................................. 10–1

Create a Custom Block ........................................................................................................................ 10–2

Create a Library Model File with the HDL Subsystem Block .................................................. 10–2

Build the HDL Subsystem Functionality .................................................................................... 10–3

Create Parameters & Functionality Using the Mask Editor ..................................................... 10–4

Generate the MATLAB Initialization Script ............................................................................... 10–7

评论0