没有合适的资源?快使用搜索试试~ 我知道了~

BCM5464数据手册

温馨提示

试读

220页

博通交换芯片数据手册

资源推荐

资源详情

资源评论

Data Sheet

BCM5464S

5464S-DS07-R

5300 California Avenue • Irvine, CA 92617 • Phone: 949-926-5000 • Fax: 949-926-5203 08/02/07

Quad 1000/100/10BASE-T Gigabit Ethernet

Transceiver

GENERAL DESCRIPTION

FEATURES

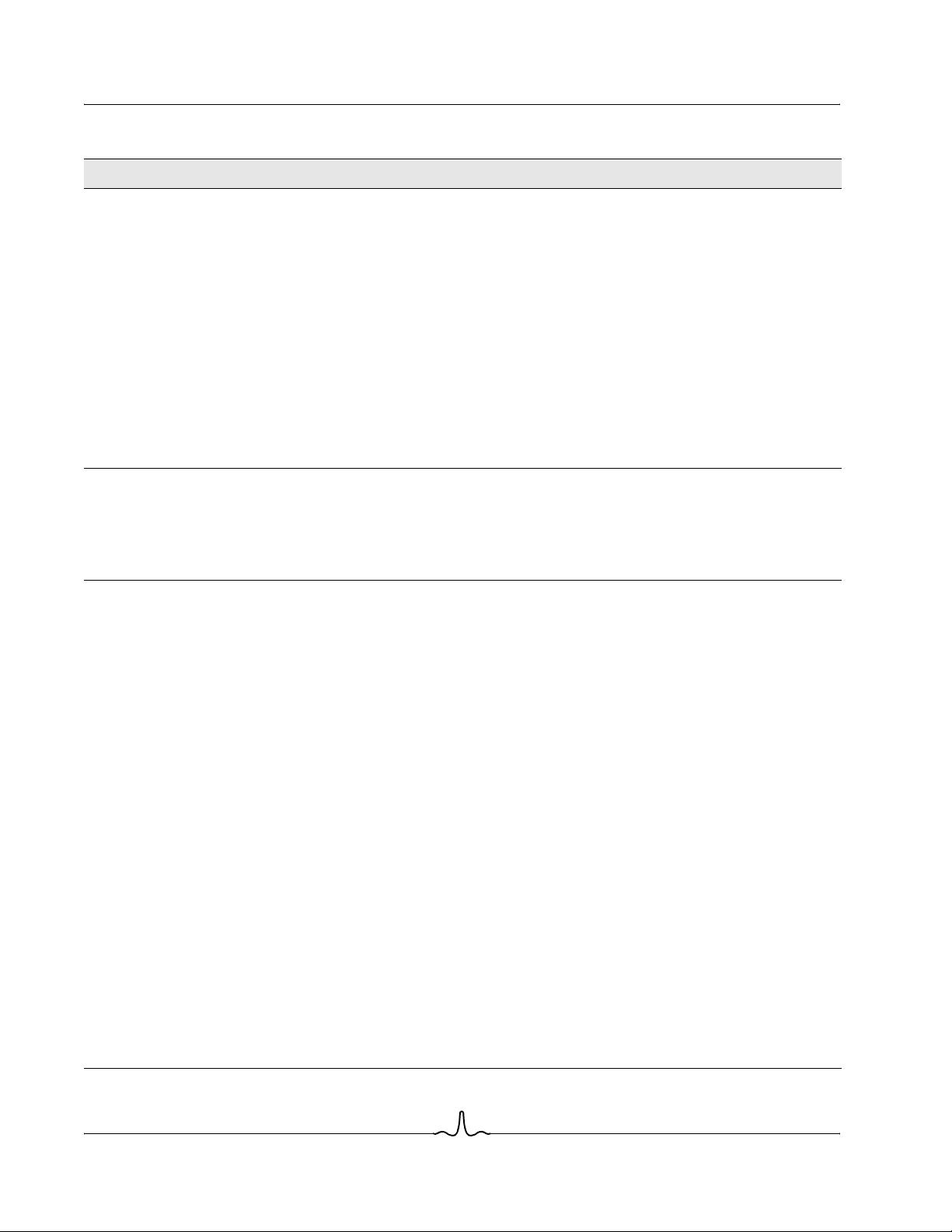

The BCM5464S transceiver consists of four triple-

speed 10/100/1000BASE-T Ethernet transceivers. The

device performs all of the physical layer functions for

1000BASE-T, 100BASE-TX and 10BASE-T Ethernet

on standard Category 5 UTP cable. The BCM5464S is

designed to be fully compliant with the SGMII, GMII,

RGMII, and RTBI industry standards. The BCM5464S

also supports a unique SerDes Pass-through mode that

allows copper or fiber support on the SerDes/SGMII

pins.

The BCM5464S is based on Broadcom’s proven digital

signal processor technology, combining digital adaptive

equalizers, ADCs, phase-locked loops, line drivers,

encoders, decoders, echo cancelers, crosstalk

cancelers and all other required support circuitry

integrated into a single monolithic CMOS chip.

Designed for reliable operation over worst-case

Category 5 cable plants, the BCM5464S automatically

negotiates with any transceiver on the opposite end of

the wire to agree on an operating speed. The PHY can

also evaluate the condition of the twisted-pair wiring to

ensure that the wiring can support operation at Gigabit

speeds, and detect and correct most common wiring

problems. The device continually monitors both the

wiring and the opposing transceiver, and alerts the

system if it detects potential problems with reliable

operation.

For single-port applications, refer to the BCM5461 or

BCM5461S data sheets.

APPLICATIONS

High-density Gigabit Ethernet switches and routers

• Support for the following line interfaces:

- 1000BASE-T IEEE 802.3ab

- 1000BASE-X IEEE 802.3z

- 100BASE-TX IEEE 802.3u

- 100BASE-FX IEEE 802.3u

- 10BASE-T IEEE 802.3

• Support for the following MAC interfaces:

- SGMII

- GMII (2.5V or 3.3V)

- RGMII (2.5V CMOS)

- RTBI (2.5V CMOS)

- SerDes

• SerDes Pass-through mode

• GMII/RGMII/RTBI trace-matched output impedance

• 3.3V or 2.5V digital I/Os

• Advanced power management

• Line-side and MAC-side loopback

• Programmable LED modes

• Cable plant diagnostics that detects cable plant

impairments

• Automatic detection and correction of wiring pair

swaps, pair skew, and pair polarity

• Robust CESD tolerance and low EMI emissions

• Support for jumbo packets up to 10 KB in size

• IEEE 1149.1 (JTAG) boundary scan

• Industrial temperature

• Package: 21 mm x 21 mm, 354-pin FPBGA

TXD[7:0]{4:1}

TX_EN{4:1}

TX_ER{4:1}

GTXCLK{4:1}

TXC{4:1}

COL{4:1}

CRS{4:1}

RX_DV{4:1}

RX_ER{4:1}

RXD[7:0]{4:1}

RXC{4:1}

SGIN(1){4:1}+

SCLK(1){4:1}+

SGOUT(1){4:1}+

MDC{4:1}

MDIO{4:1}

MODES

LED[4:1]{4:1}

SYMBOL ENCODER

SYMBOL DECODER/

ALIGNER

LED DRIVERS

MII MGMT

CONTROL

MII REGISTERS

VOLTAGE

REGULATOR

BIAS GENGERATOR

CLOCK

GENERATOR

AUTO-

NEGOTIATION

TX DAC

BASELINE

WANDER

CORRECTION

XTALK

CANCELLER

DFE &

TRELLIS

DECODER

TIMING & PHASE

RECOVERY

ECHO

CANCELLER

FFE

ADC

PGA

TRD[3:0]{4:1}+

XTALI

XTALO

RDAC

REGSUP[2:1]

REGCNTL[2:1]

REGSEN[2:1]

PTOUT(1){4:1}+

PTIN(1){4:1}+

SerDes Pass-

Through

SERIAL/SGMII

BCM5464S Data Sheet

08/02/07

Broadcom Corporation

Page ii Document 5464S-DS07-R

REVISION HISTORY

Revision Date Description

5464S-DS07-R 08/02/07 Updated:

• ”Reduced 10-Bit Interface” on page 3.

• Mode Select text in Table 2, ”Ball Descriptions,” on page 12.

• Table 124, ”Ordering Information,” on page 187.

Added:

• Descriptive text in ”Standby Power-Down Mode” on page 34.

• Descriptive text in ”Misc. 1000BASE-X Status” on page 127.

• Figure 19, ”SGMII Differential Output Voltage,” on page 182

• Figure 20, ”SGMII Differential Input Voltage,” on page 182

• Figure 21, ”Fiber Differential Output Voltage,” on page 182

• Figure 22, ”Fiber Differential Input Voltage,” on page 183

Removed:

• Figure 24, “SGMII DC Parameters”

• Figure 25, “Fiber DC Parameters”

5464S-DS06-R 01/24/06 Updated:

• The Default for bits 4 and 12 from

0

to

ER pin

in Table 49, ”1000BASE-T/100BASE-

TX/10BASE-T Auxiliary Control Register (Address 18h, Shadow Value 000),” on

page 111.

Added:

•

A1

to the Part Numbers in Table 124, ”Ordering Information,” on page 215.

5464S-DS05-405-R 04/07/05 Updated:

• “Ball Descriptions” table.

• “RTBI Interface.”

• “LED Interface.”

• “1000BASE-T/100BASE-TX/10BASE-T Next Page Transmit” register.

• “1000BASE-T/100BASE-TX/10BASE-T Link Partner Received Next Page” register.

• “1000BASE-T/100BASE-TX/10BASE-T PHY Extended Control” register.

• “1000BASE-T/100BASE-TX/10BASE-T Auxiliary Status Summary” register.

• “1000BASE-T/100BASE-TX/10BASE-T Spare Control 1” register.

• “1000BASE-T/100BASE-TX/10BASE-T Spare Control 3” register.

• “Auxiliary 1000BASE-X Control” register.

• “1000BASE-T/100BASE-TX/10BASE-T Mode Control” register.

• “1000BASE-T/100BASE-TX/10BASE-T Test Register 1” register.

• “1000BASE-X Auto-Negotiation Link Partner Ability” register.

• “Management Interface Timing.”

• “RGMII/RTBI Input Timing (Normal Mode): GTXCLK and TXD[3:0].”

• “Fiber Receive Jitter Tolerance.”

• “Absolute Maximum Ratings.”

• “DC Characteristics.”

• “Thermal Information” to “Packaging Information.”

Added:

• “Twisted Pair Low-Power Mode of Operation.”

• “JTAG Timing.”

• “Pb-Free Packaging.”

Data Sheet BCM5464S

08/02/07

Broadcom Corporation

Document 5464S-DS07-R Page iii

5464S-DS04-R 02/25/04 Updated:

• BCM5461 and BCM5461S for BCM5421 and BCM5421S.

• In “Hardware Signal Descriptions”:

- INTF_SEL[3:0] from CS to SOR.

- TEST[1:0].

- OVDD (When in SGMII mode use 2.5V supply).

• In “Operational Description”:

- Auto Power-Down Mode

- LED

• Swap RX MDIX from RO to R/W in register 18-4.4.

• RGMII Out-of-Band Status Disable to RGMII In-Band Status Disable and change

description in register 18-7.5.

Revision Date Description

BCM5464S Data Sheet

08/02/07

Broadcom Corporation

Page iv Document 5464S-DS07-R

5464S-DS04-R

(Cont.)

02/25/04 Updated (Cont.):

• SD invert description to say it only applies to 1000BASE-X and not to 100BASE-FX

mode in register 1C-30.8.

• In “AC Timing”:

- MII TX 10M Timing: TXC_TXEN_HOLD min. from 10 ns to 0 ns.

- MII 10M TX Timing Figure: TXC_TXEN_HOLD and TXC_TXEN_VALID.

- 1000BASE-T TX_EN assert to TRD from 80 to 84 ns (IEEE spec).

- 1000BASE-T Receive CRS, COL assert after TRD±{3:0} from 5 ns to 240 ns.

- GTXCLK to TXD RGMII (Normal) setup time from 200 ps to 1000 ps.

- GTXCLK to TXD RGMII (Delay) setup time from -1700 ps to -1900 ps.

• In “DC”:

- Split “SGMII” and “SerDes” into two sections

- Changed Maximum Input Differential Voltage from 800 mV to 2000 mV for both

SGMII and SerDes

• Theta JA, TC, TB in “Thermal Information.”

Added:

• To cover page:

- Industrial Temp.

- 100BASE-FX mode

- 2.5V GMII operation

• To “Functional Description”:

- 2.5V GMII and MII operation

- 10/100BASE-T Forced Mode Auto-MDIX

- Jumbo Packets

• 100BASE-FX to pin description in “Hardware Signal Descriptions.”

• To “Operational Description”:

- 100BASE-FX Mode

- RGMII in-band description

• 1000BASE-X register descriptions to register 11.

• 1000BASE-X register descriptions to register 12.15:0.

• To register 13.15:0, register descriptions for:

- 1000BASE-X

- Receive Packet Transmit Error Code Counter

• 1000BASE-X register descriptions to Register 14.15:0.

• In “AC Timing”:

- Fiber and SGMII Receive jitter specs

- Fiber and SGMII transmit specs

• GMII to RGMII 2.5V spec. to “DC.”

• To “Thermal Information”:

- Psi-JT numbers for junction temperature calculations

- Industrial temp.

5464S-DS03-R 01/07/03 Updated:

• “Ball Descriptions” table.

•

Revision Date Description

Data Sheet BCM5464S

08/02/07

Broadcom Corporation

Document 5464S-DS07-R Page v

5464S-DS02-R 12/18/02

Updated:

• “General Description.”

• “Features.”

• “Modes of Operation.”

• “Reduced Gigabit Media Independent Interface.”

• “Reduced 10-Bit Interface.”

• “Ball Descriptions” table.

• “354-Pin FPBGA Ballout” table.

• “Resetting the BCM5220.”

• “RGMII Interface.”

• “LED Interface.”“LED Modes (Except in SerDes-Copper Media Converter Mode)”

table.

• “1000BASE-T/100BASE-TX/10BASE-T PHY Extended Status Register (Address

11h)” table.

• “1000BASE-T/100BASE-TX/10BASE-T Misc Control Register (Address 18h,

Shadow Value 111)” table.

• “1000BASE-T/100BASE-TX/10BASE-T Spare Control 2 Register (Address 1Ch,

Shadow Value 00100)” table.

• “Auto Power-Down Register (Address 1Ch, Shadow Value 01010)” table.

• “1000BASE-T/100BASE-TX/10BASE-T LED Selector 1 Register (Address 1Ch,

Shadow Value 01101)” table.

• “ 1000BASE-T/100BASE-TX/10BASE-T LED Selector 2 Register (Address 1Ch,

Shadow Value 01110)” table.

• “1000BASE-T/100BASE-TX/10BASE-T HCD Status Register (Address 1Dh) Bit 15

=1” table.

• “SGMII Timing” table.

• “DC Characteristics” table.

• “SGMII DC Parameters” figure.

• “Thermal Information” and “354-Pin FPBGA Theta

JA

vs. Air Flow” table.

• “Mode Selection” table with “Hardware Mode Selection” and “Software Mode

Selection” tables.

Added:

• “Board/Thermal Land Design Recommendations for 354-Pin FPBGA.”

5464S-DS01-R 08/30/02 Updated:

• General cleanup.

5464S-DS00-R 03/29/02 Initial release.

Revision Date Description

剩余219页未读,继续阅读

资源评论

v52332015-07-17broadcom的资料很难找的

v52332015-07-17broadcom的资料很难找的

sunyore

- 粉丝: 0

- 资源: 12

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功