1 Overview

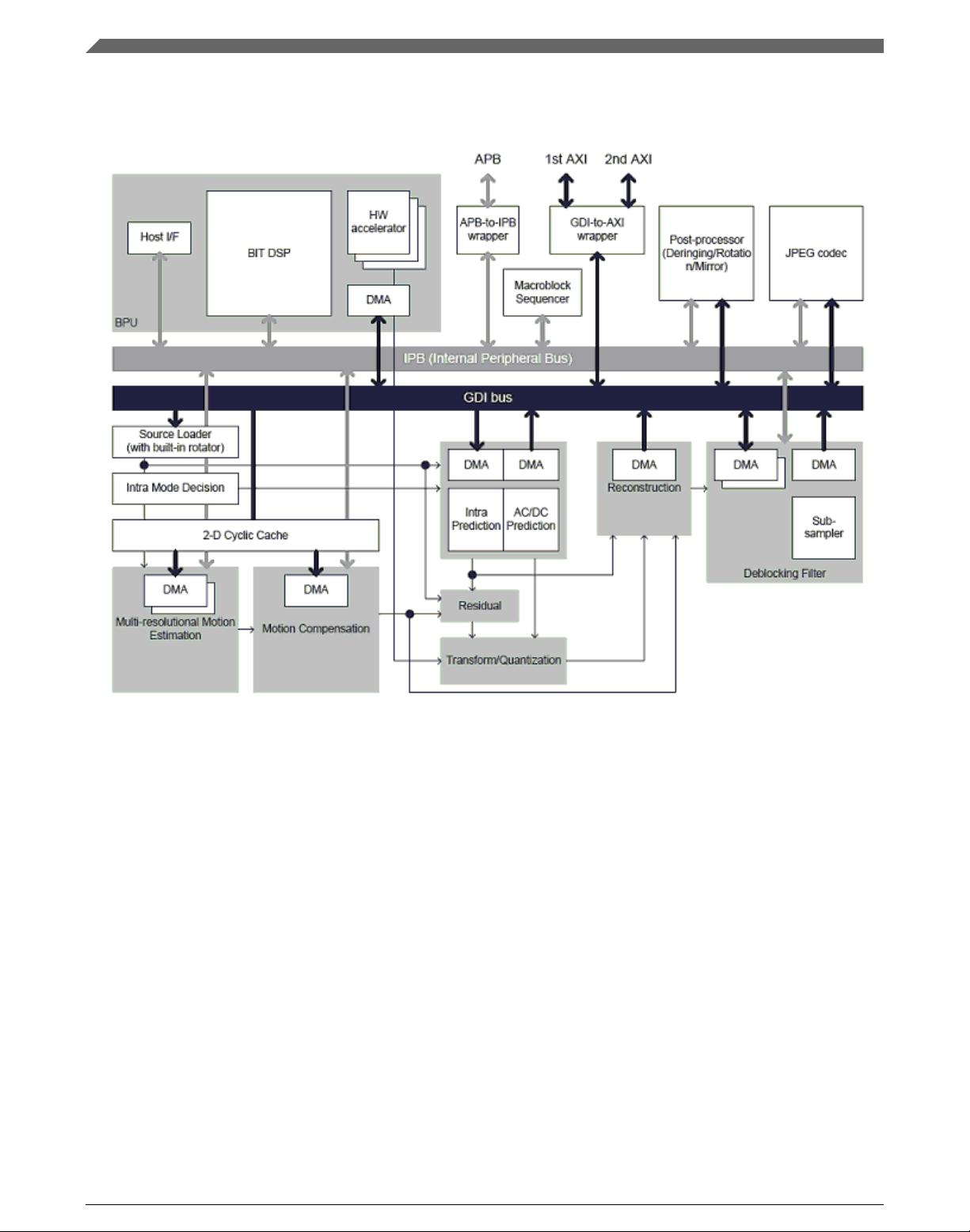

i.MX 6Dual/6Quad Video Processing Unit (VPU) is a high

performance multi-standard video decoder and encoder engine

that performs multiple standard decoding and encoding

operations. VPU codec is fully compliant with H.264 BP/MP/

HP, VC-1 SP/MP/AP, MPEG-4 SP/ASP except GMC, DivX

(Xvid), MPEG-1/2, VP8, AVS and MJPEG decoding and H.

264, MPEG-4, H.263, and MJPG encoding. VPU supports up

to full HD 1920x1080 60i or 30p decoding and 1920x1088

encoding. It can encode or decode multiple video clips with

multiple standards simultaneously. A block diagram of the

i.MX 6Dual/6Quad VPU is shown in figure below.

VPU connects with the system through the 32-bit AMBA3

APB bus for system control and the 64-bit AMBA3 AXI for

data throughput. VPU also takes advantage of on-chip

memories to achieve high performance.

Most video hardware blocks in VPU are optimally designed

for shared usage between different video standards which

provides ultra low power and low gate count with powerful

performance. As shown in figure below, VPU has a 16-bit

DSP core, the BIT processor, which controls the internal video

codec operations.

For simple and efficient control of the VPU by the host

processor, VPU provides a set of registers called the host

interface registers. Most commands and responses between the

host processor and the VPU are transmitted through the host

interface registers. Stream data and some output picture data

Freescale Semiconductor

Document Number:IMX6VPUAPI

Rev. L3.0.35_1.1.0, 01/2013

i.MX 6Dual/6Quad VPU Application

Programming Interface Linux

Reference Manual

© 2013 Freescale Semiconductor, Inc.

Contents

1 Overview....................................................................1

2 Host Interface............................................................5

3 API Features..............................................................7

4 VPU Control...........................................................68