DesignWare Library

DW8051 MacroCell

Data Sheet

Overview

The DesignWare

®

DW8051

™

MacroCell is a high-performance, configurable, fully synthesizable 8051 core that is binary compatible with

the industry standard 803x/805x microcontrollers. The DW8051 core is technology-independent and has been fabricated in both ASIC

and FPGA technologies. Designed for ease of use, the DW8051 includes the coreConsultant

™

tool, a user-friendly wizard, which guides

users through configuration, simulation and synthesis.

The DesignWare DW8051 MacroCell solution includes the DW8051 MacroCell, a reference design, and Synopsys’ extensive verification

environment. The high-performance architecture of the DW8051 provides up to three times performance improvement over the standard

8051 when operating at the same clock rate.

P

roven Quality

, Complete Solution

To ensure quality, the DW8051 was

developed accor

ding to Synopsys’ strict

design-for-reuse methodology. It has

under

gone extensive testing during the

design process and has been proven in

many different technologies. It has also

been tested with a variety of third-party

8051 development tools and 8051

evaluation boar

ds.

The DW8051’s high-performance, config-

urable, synthesizable ar

chitectur

e, combined

with the development environment, provides

a total solution for building low-cost, high-

per

for

mance embedded control systems

for a wide range of applications.

A

utomated Design Flow with Synopsys

coreConsultant

The DW80

51 MacroCell solution includes

the Synopsys coreConsultant tool, which

pr

ovides the following ser

vices:

n

Activity checklist that guides users

through DW8051 design activities in

the correct order

n

Automatic, error-free DW8051

configuration,

including parameter

cr

oss-dependency checking

n

Automatic configuration and operation

of the DW8051 verification environment

n

Automatic, high-quality synthesis with

users’ technology library and installed

version of Design Compiler

™

n

Automatic design checking and synthesis

results analysis

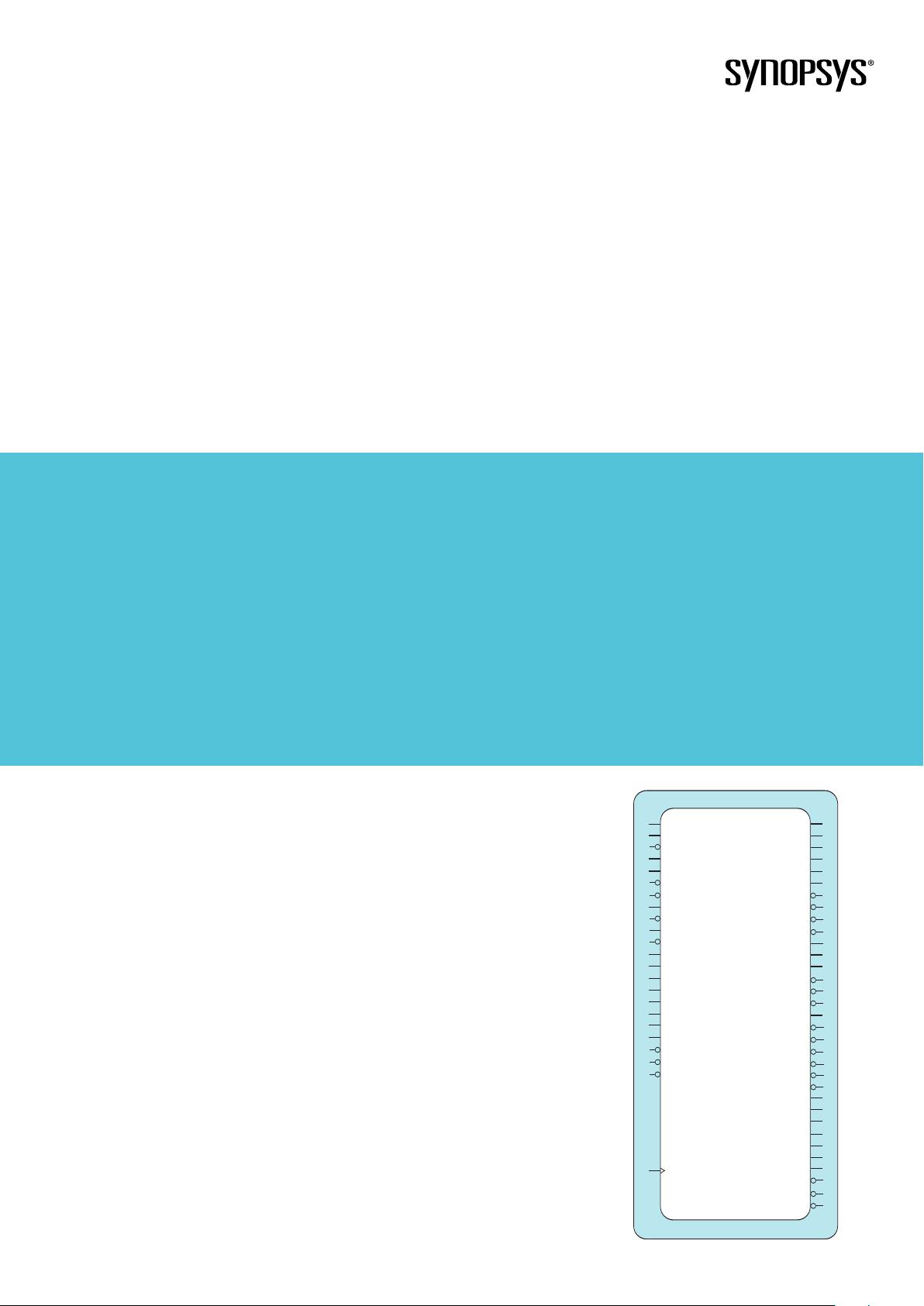

DW8051

sfr_data_in

mem_data_in

mem_ea_n

iram_data_out

irom_data_out

int0_n

int1_n

int2

int3_n

int4

int5_n

pfi

wdti

t0

t1

t2

t2ex

rxd0_in

rxd1_in

test_mode_n

rst_in_n

por_n

clk

sfr_addr

sfr_data_out

sfr_wr

str_rd

mem_addr

mem_data_out

mem_wr_n

mem_rd_n

mem_pswr_n

mem_psrd_n

mem_ale

iram_addr

iram_data_in

iram_rd_n

iram_we1_in

iram_we2_n

irom_addr

irom_rd_n

irom_cs_n

port_pin_reg_n

p0_mem_reg_n

p0_addr_data_n

p2_mem_reg_n

txd0

rxd0_out

txd1

rxd1_out

t0_out

t1_out

t2_out

stop_mode_n

idle_mode_n

rst_out_n

DW8

051 Input/Output Signals

- 1

- 2

- 3

前往页