没有合适的资源?快使用搜索试试~ 我知道了~

ATmega8515(L)_cn

需积分: 10 1 下载量 176 浏览量

2011-08-03

11:41:54

上传

评论

收藏 2.25MB PDF 举报

温馨提示

试读

241页

ATmega8515(L)_cn的中文资料

资源详情

资源评论

资源推荐

2512F–AVR–12/03

产品特性

• 高性能、低功耗的 8 位 AVR

®

微处理器

• RISC 结构

– 130 条指令 – 大多数指令执行时间为单个时钟周期

–32个 8 位通用工作寄存器

– 全静态工作

– 工作于 16 MHz 时性能高达 16 MIPS

– 只需两个时钟周期的硬件乘法器

• 非易失性程序和数据存储器

–8K字节的系统内可编程 Flash

擦写寿命 : 10,000 次

– 具有独立锁定位的可选 Boot 代码区

通过片上 Boot 程序实现系统内编程

真正的同时读写操作

– 512 字节的 EEPROM

擦写寿命 : 100,000 次

– 512 字节的片内 SRAM

– 达到 64K 字节的可选外部 存储器空间

– 可以对锁定位进行编程以实现用户程序的加密

• 外设特点

– 具有独立预分频器和比较器功能的 8 位定时器 / 计数器

– 一个具有预分频器、比较功能和捕捉功能的 16 位定时器 / 计数器

– 三通道 PWM

– 可编程的串行 USART

– 可工作于主机 / 从机模式的 SPI 串行接口

– 具有独立片内振荡器的可编程看门狗定时器

– 片内模拟比较器

• 特殊的处理器特点

– 上电复位以及可编程的掉电检测

– 片内经过标定的 RC 振荡器

– 片内 / 片外中断源

– 三种睡眠模式 : 空闲模式、掉电模式及 Standby 模式

• I/O 和封装

–35个可编程的 I/O 口线

–40引脚 PDIP 封装 , 44 引脚 TQFP 封装 ,44 引脚 PLCC 封装与 44 引脚 MLF 封装

• 工作电压 :

– ATmega8515L:2.7 - 5.5V

– ATmega8515:4.5 - 5.5V

• 速度等级

– 0 - 8 MHz ATmega8515L

– 0 - 16 MHz ATmega8515

具有 8KB 系统内

可编程 Flash 的

8 位 微

控制器

ATmega8515

ATmega8515L

本文是英文数据手册的中文

翻译,其目的是方便中国用

户的阅读。它无法自动跟随

原稿的更新,同时也可能存

在翻译上的错误。读者应该

以英文原稿为参考以获得更

准确的信息。

Rev. 2512F–AVR–12/03

2

ATmega8515(L)

2512F–AVR–12/03

引脚配置

Figure 1. ATmega8515 的引脚

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

(OC0/T0) PB0

(T1) PB1

(AIN0) PB2

(AIN1) PB3

(SS) PB4

(MOSI) PB5

(MISO) PB6

(SCK) PB7

RESET

(RXD) PD0

(TDX) PD1

(INT0) PD2

(INT1) PD3

(XCK) PD4

(OC1A) PD5

(WR) PD6

(RD) PD7

XTAL2

XTAL1

GND

VCC

PA0 (AD0)

PA1 (AD1)

PA2 (AD2)

PA3 (AD3)

PA4 (AD4)

PA5 (AD5)

PA6 (AD6)

PA7 (AD7)

PE0 (ICP/INT2)

PE1 (ALE)

PE2 (OC1B)

PC7 (A15)

PC6 (A14)

PC5 (A13)

PC4 (A12)

PC3 (A11)

PC2 (A10)

PC1 (A9)

PC0 (A8)

PDIP

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

(MOSI) PB5

(MISO) PB6

(SCK) PB7

RESET

(RXD) PD0

NC*

(TXD) PD1

(INT0) PD2

(INT1) PD3

(XCK) PD4

(OC1A) PD5

PA4 (AD4)

PA5 (AD5)

PA6 (AD6)

PA7 (AD7)

PE0 (ICP/INT2)

NC*

PE1 (ALE)

PE2 (OC1B)

PC7 (A15)

PC6 (A14)

PC5 (A13)

44

43

42

41

40

39

38

37

36

35

34

12

13

14

15

16

17

18

19

20

21

22

(WR) PD6

(RD) PD7

XTAL2

XTAL1

GND

NC*

(A8) PC0

(A9) PC1

(A10) PC2

(A11) PC3

(A12) PC4

PB4 (SS)

PB3 (AIN1)

PB2 (AIN0)

PB1 (T1)

PB0 (OC0/T0)

NC*

VCC

PA0 (AD0)

PA1 (AD1)

PA2 (AD2)

PA3 (AD3)

TQFP/MLF

7

8

9

10

11

12

13

14

15

16

17

39

38

37

36

35

34

33

32

31

30

29

(MOSI) PB5

(MISO) PB6

(SCK) PB7

RESET

(RXD) PD0

NC*

(TXD) PD1

(INT0) PD2

(INT1) PD3

(XCK) PD4

(OC1A) PD5

PA4 (AD4)

PA5 (AD5)

PA6 (AD6)

PA7 (AD7)

PE0 (ICP/INT2)

NC*

PE1 (ALE)

PE2 (OC1B)

PC7 (A15)

PC6 (A14)

PC5 (A13)

6

5

4

3

2

1

44

43

42

41

40

18

19

20

21

22

23

24

25

26

27

28

(WR) PD6

(RD) PD7

XTAL2

XTAL1

GND

NC*

(A8) PC0

(A9) PC1

(A10) PC2

(A11) PC3

(A12) PC4

PB4 (SS)

PB3 (AIN1)

PB2 (AIN0)

PB1 (T1)

PB0 (OC0/T0)

NC*

VCC

PA0 (AD0)

PA1 (AD1)

PA2 (AD2)

PA3 (AD3)

PLCC

NOTES:

1. MLF bottom pad should be soldered to ground.

2. * NC = Do not connect

(

Ma

y

be used in future devices

)

3

ATmega8515(L)

2512F–AVR–12/03

综述 ATmega8515是基于增强的AVR RISC结构的低功耗8位CMOS 微控制器。由于其先进的

指令集以及单时钟周期指令执行时间,ATmega8515 的数据吞吐率高达 1MIPS/MHz,从

而可以缓减系统在功耗和处理速度之间的矛盾。

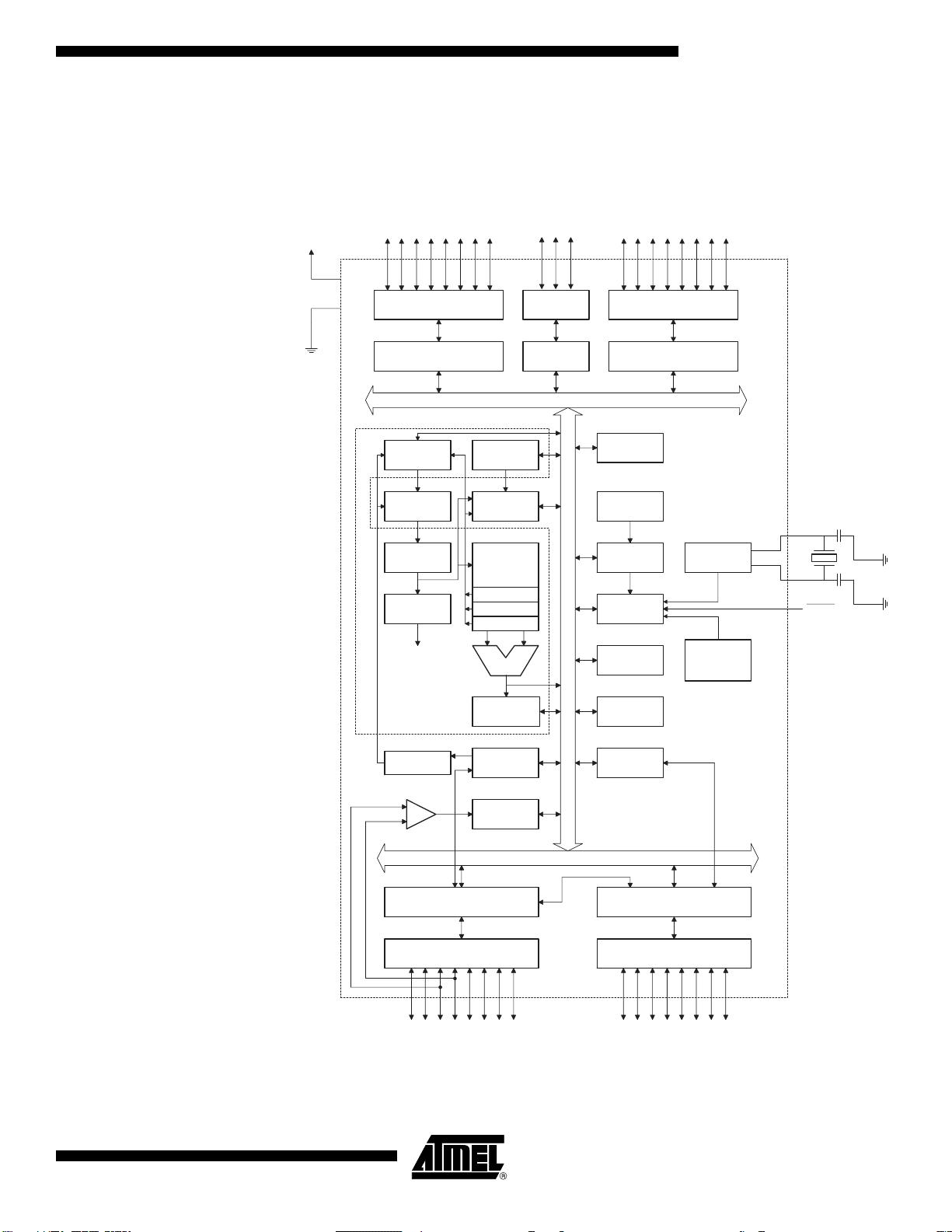

方框图 Figure 2. 结构框图

INTERNAL

OSCILLATOR

WATCHDOG

TIMER

MCU CTRL.

& TIMING

OSCILLATOR

TIMERS/

COUNTERS

INTERRUPT

UNIT

STACK

POINTER

EEPROM

SRAM

STATUS

REGISTER

USART

PROGRAM

COUNTER

PROGRAM

FLASH

INSTRUCTION

REGISTER

INSTRUCTION

DECODER

PROGRAMMING

LOGIC

SPI

COMP.

INTERFACE

PORTA DRIVERS/BUFFERS

PORTA DIGITAL INTERFACE

GENERAL

PURPOSE

REGISTERS

X

Y

Z

ALU

+

-

PORTC DRIVERS/BUFFERS

PORTC DIGITAL INTERFACE

PORTB DIGITAL INTERFACE

PORTB DRIVERS/BUFFERS

PORTD DIGITAL INTERFACE

PORTD DRIVERS/BUFFERS

XTAL1

XTAL2

RESET

CONTROL

LINES

V

CC

GND

PA0 - PA7 PC0 - PC7

PD0 - PD7PB0 - PB7

AVR CPU

INTERNAL

CALIBRATED

OSCILLATOR

PORTE

DRIVERS/

BUFFERS

PORTE

DIGITAL

INTERFACE

PE0 - PE2

4

ATmega8515(L)

2512F–AVR–12/03

AVR 内核具有丰富的指令集和 32 个通用工作寄存器。所有的寄存器都直接与算逻单元

(ALU) 相连接,使得一条指令可以在一个时钟周期内同时访问两个独立的寄存器。这种结

构大大提高了代码效率,并且具有比普通的 CISC 微控制器最高至 10 倍的数据吞吐率。

ATmega8515 有如下特点 :8K 字节的系统内可编程 Flash( 具有同时读写的能力,即

RWW),512 字节 EEPROM,512 字节 SRAM,一个外部存储器接口,35 个通用 I/O 口线,

32 个通用工作寄存器,两个具有比较模式的灵活的定时器/ 计数器(T/C),片内 /外中断,可

编程串行 USART,具有片内振荡器的可编程看门狗定时器,一个 SPI 串行端口,以及三

个可以通过软件进行选择的省电模式。工作于空闲模式时 CPU 停止工作,而 SRAM、

T/C、 SPI 端口以及中断系统继续工作;掉电模式时晶体振荡器停止振荡,所有功能除了

中断和硬件复位之外都停止工作; Standby 模式下只有晶体或谐振振荡器运行,其余功能

模块处于休眠状态,使得器件只消耗极少的电流,同时具有快速启动能力。

本芯片是以 Atmel 高密度非易失性存储器技术生产的。片内 ISP Flash 允许程序存储器通

过 ISP 串行接口,或者通用编程器进行编程,也可以通过运行于 AVR 内核之中的引导程

序进行编程。引导程序可以使用任意接口将应用程序下载到应用Flash存储区(Application

Flash Memory)。在更新应用Flash存储区时引导Flash区(Boot Flash Memory)的程序继续

运行,实现了 RWW 操作。 通过将 8 位 RISC CPU 与系统内可编程的 Flash 集成在一个

芯片内, ATmega8515 成为一个功能强大的单片机,为许多嵌入式控制应用提供了灵活

而低成本的解决方案。

ATmega8515 具有一整套的编程与系统开发工具,包括:C 语言编译器、宏汇编、 程序调

试器 / 软件仿真器、仿真器及评估板。

声明 本数据手册的典型值来源于对器件的仿真,以及其他基于相同产生工艺的 AVR 微控制器

的标定特性。本器件经过特性化之后将给出实际的最大值和最小值。

AT90S4414/8515 与

ATmega8515 兼容性

ATmega8515除有AT90S4414/8515的所有特性外,还有一些新的特性。ATmega8515 基

本上对 AT90S4414/8515 向下兼容。但两者间还会存在不兼容的问题。可通过对

AT90S4414/8515 的 S8515C 熔丝位编程,选择兼容模式来解决该问题,ATmega8515 引

脚与 AT90S4414/8515 引脚 100% 兼容,也可在电路印刷板上替换 AT90S4414/8515,

但二者的熔丝位位置及电气特性间存在差异。

AT90S4414/8515 兼容模式 对 S8515C 熔丝位编程会改变下列功能:

• 改变看门狗溢出周期的时序禁用,详见 P49“ 改变看门狗定时器配置的时间序列 ” 。

•USART接收寄存器的双缓冲器被禁用,详见 P127“AVR USART 和 AVR UART – 兼

容性 ” 。

• PORTE(2:1) 将设为输出,而 PORTE0 会设为输入。

5

ATmega8515(L)

2512F–AVR–12/03

引脚说明

VCC 数字电路的电源

GND 地

端口 A(PA7..PA0) 端口 A 为 8 位双向 I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特

性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉

低时将输出电流。在复位过程中,即使系统时钟还未起振,端口 A 处于高阻状态。

端口 A 的其他功能见 P63。

端口 B(PB7..PB0) 端口 B 为 8 位双向 I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特

性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉

低时将输出电流。在复位过程中,即使系统时钟还未起振,端口 B 处于高阻状态。

端口 B 的其他功能见 P63。

端口 C(PC7..PC0) 端口 C 为 8 位双向 I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特

性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉

低时将输出电流。在复位过程中,即使系统时钟还未起振,端口 C 处于高阻状态。

端口 D(PD7..PD0) 端口 D 为 8 位双向 I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特

性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电路

拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口 D 处于高阻状态。

端口 D 的其他功能见 P68。

端口 E(PE2..PE0) 端口 E 为 3 位双向 I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特

性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电路

拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口 E 处于高阻状态。

端口 E 的其他功能见 P70。

R

ESET 复位输入引脚。持续时间超过最小门限时间的低电平将引起系统复位。门限时间见

P42Table 18。持续时间小于门限时间的脉冲不能保证可靠复位。

XTAL1 反向振荡放大器与片内时钟操作电路的输入端。

XTAL2 反向振荡放大器的输出端。

代码例子 本数据手册包含了一些简单的代码例子以说明如何使用芯片各个不同的功能模块。这些

例子都假定在编译之前已经包含了正确的头文件。有些 C 编译器在头文件里并没有包含

位定义,而且各个 C 编译器对中断处理有自己不同的处理方式。请注意查阅相关文档以

获取具体的信息。

剩余240页未读,继续阅读

lortbeyond

- 粉丝: 1

- 资源: 5

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0