EDA 实验报告 电子 033 班 刘宇 20032660

实验八 数字钟设计实验

一、 实验目的:

1. 学习数字钟的基本原理

2. 学习数字钟的基本设计方法

3. 学习数字钟的校时控制的基本设计方法

4. 学习数字钟的可变进制计数器的设计方法

5. 掌握采用 VHDL 语言设计频率测量和周期测量

二、 实验原理

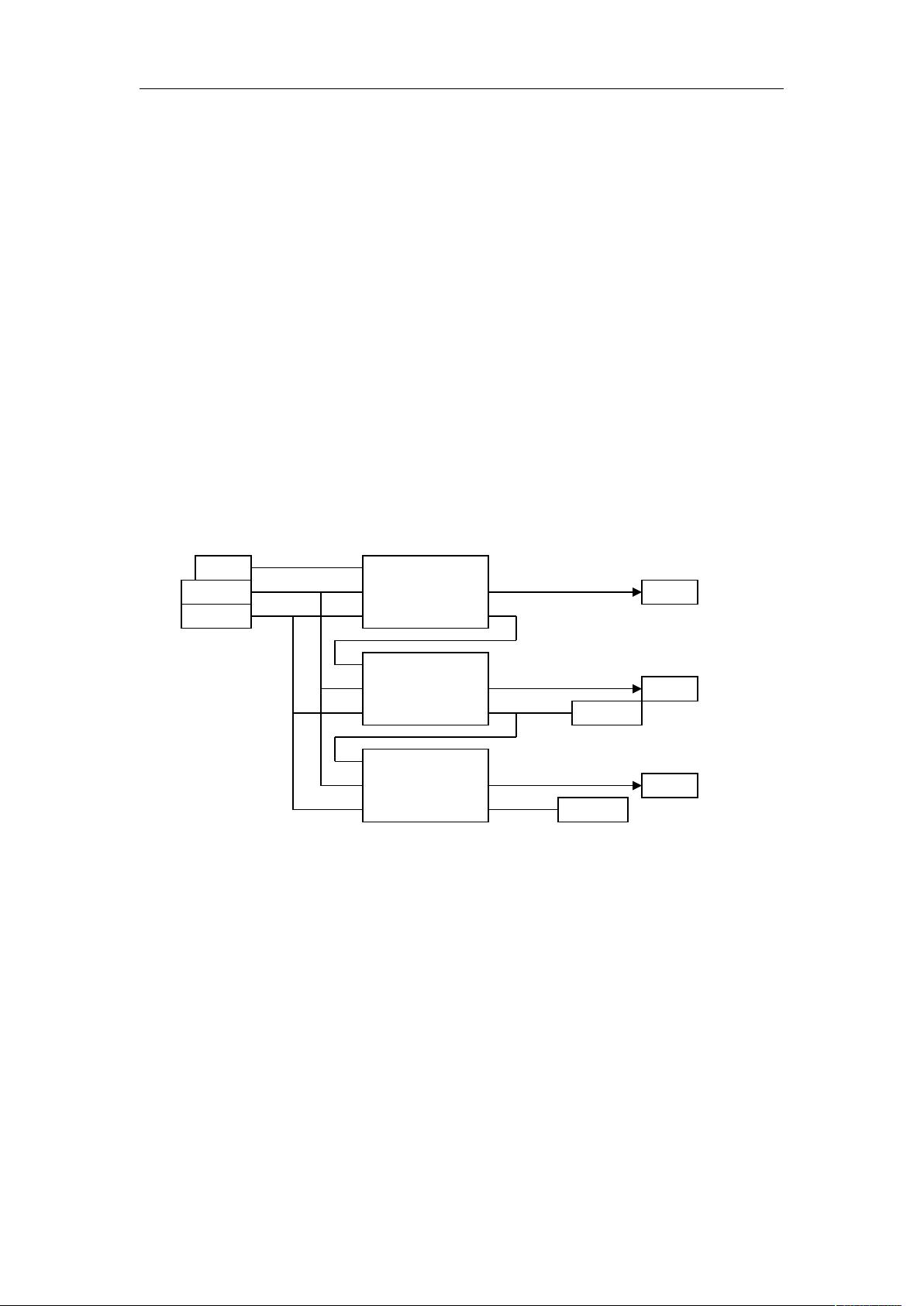

数字钟的主要功能有年月日时分秒的显示输出功能和对日期及时间进行设置的功

能,还可以有整点报时等功能。设计数字钟的核心问题是时钟日期的自动转换功能。

即自动识别不同月份的天数的控制。据此可以设计一个如图所示结构的数字钟,该数

字钟包括校时模块、月份天数处理模块、时分秒计时模块、年月日模块和输出选择模

块。在本实验中,只进行了简单的数字时分秒设计,其他部分还有待下一步改进。

三、 实验内容:

1. 据图设计数字钟的各模块

2. 方针实验结果

3. 用 VHDL 语言完成设计

四、 实验源程序:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

1

clk

set 60 进制

d_in qc

clk

set 60 进制

d_in qc

clk

set 24 进制

d_in qc

整点报时

秒输出

分输出

时输出

秒脉冲

校时电平

校时电平

进位输出