VGA/LCD Core

v2.0

Specifications

Author: Richard Herveille

rherveille@opencores.org

Document rev. 1.2

March 20, 2003

This page left intentionally blank

OpenCores Enhanced VGA/LCD Core Datasheet 3/20/2003

www.opencores.org Rev 1.2 Preliminary

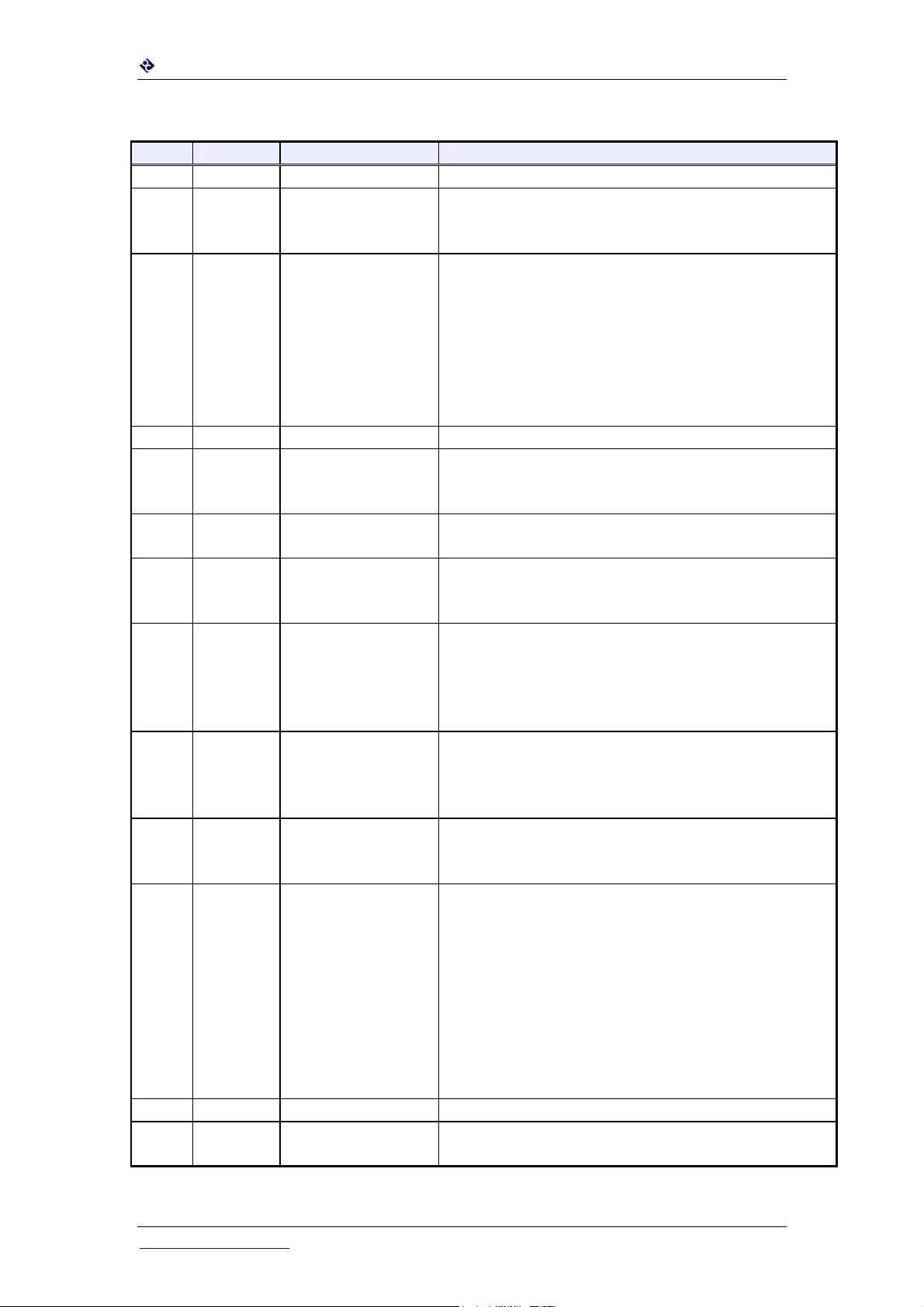

Revision History

Rev. Date Author Description

0.1 10/04/01 Richard Herveille First Draft

0.1a 20/04/01 Richard Herveille Changed proposal to specifications

Added Appendix A

Extended Register Specifications

0.2 21/05/01 Richard Herveille First official release

Added OpenCores logo

Changed Chapter 1, Introduction

Finished Chapter 2, IO ports

Finished Chapter 3, Registers

Extended Chapter 4, Operation

Changed Chapter 5, Architecture

Added Appendix B

0.3 28/05/01 Richard Herveille Fixed some inconsistencies.

0.4 03/06/01 Richard Herveille Changed all references to address related subjects

(core fix & documentation fix).

Added Appendix C

0.4a 04/06/01 Richard Herveille Fixed some minor typing errors in the document

(credits: Rudolph Usselmann)

0.5 15/07/01 Richard Herveille Added Color Lookup Table bank switching.

Added embedded CLUT section.

Revised horizontal & vertical timing section.

0.6 31/07/01 Richard Herveille Added Power-on-Reset description.

Changed CBSE & VBSE bits functionality.

Added Bank Switch Section.

Added VGA & CLUT section to Appendix B.

Changed introduction page.

0.7 10/19/01 Richard Herveille Major VGA/LCD Core changes; core v2.0.

Changed Manual to reflect core changes.

Removed all references to external CLUT

v2.0 core has CLUT internally.

0.8 28/01/02 Richard Herveille Fixed some typos.

Added 32bpp mode.

Added Bandwidth Issues section.

1.0 28/03/02 Richard Herveille Expanded Bandwidth Issues section.

Added Hardware Cursor sections.

Added Table of Contents.

Added Appendix-D.

Changed Architecture section.

Changed Operation section.

Changed introduction page.

Changed table headers.

Added OpenCores logo to page header.

Revised entire document.

1.1 20/04/02 Richard Herveille Changed VGA timing section.

1.2 18/03/03 Richard Herveille Added support for WISHBONE revB.3

Synchronous Registered Feedback Cycles.

OpenCores Enhanced VGA/LCD Core Datasheet 3/20/2003

www.opencores.org Rev 1.2 Preliminary

Table of contents

INTRODUCTION........................................................................................................1

IO PORTS.....................................................................................................................2

2.1 CORE PARAMETERS...............................................................................................2

2.2 WISHBONE SYSCON INTERFACE CONNECTIONS .................................................2

2.3 WISHBONE SLAVE INTERFACE CONNECTIONS ...................................................3

2.4 WISHBONE MASTER INTERFACE CONNECTIONS ................................................4

2.5 VGA PORT CONNECTIONS ....................................................................................5

REGISTERS.................................................................................................................7

3.1 REGISTERS LIST.....................................................................................................7

3.2 ACCESSING RESERVED ADDRESS LOCATIONS .......................................................7

3.3

CONTROL REGISTER [CTRL] ................................................................................8

3.4

STATUS REGISTER [STAT]..................................................................................13

3.5 HORIZONTAL TIMING REGISTER [HTIM] ............................................................14

3.6 VERTICAL TIMING REGISTER [VTIM].................................................................15

3.7 HORIZONTAL AND VERTICAL LENGTH REGISTER [HVLEN] ...............................15

3.8 VIDEO BASE ADDRESS [VBARA] [VBARB].......................................................16

3.9 HARDWARE CURSOR BASE ADDRESS [C0BAR] [C1BAR] .................................17

3.10 HARDWARE CURSOR (X,Y) REGISTER [C0XY] [C1XY]...................................17

3.11 HARDWARE CURSOR COLOR REGISTERS [C0CR] [C1CR]................................17

3.12 8BPP PSEUDO COLOR LOOKUP TABLE [PCLT]..................................................18

OPERATION..............................................................................................................19

4.1 VIDEO TIMING .....................................................................................................19

4.1.1 HORIZONTAL VIDEO TIMING ............................................................................19

4.1.2 VERTICAL VIDEO TIMING.................................................................................20

4.1.3 COMBINED VIDEO FRAME TIMING....................................................................21

4.2

PIXEL COLOR GENERATION.................................................................................22

4.2.1

COLOR PROCESSOR INTERNALS........................................................................22

4.2.2

ADDRESS GENERATOR .....................................................................................22

4.2.3

DATA BUFFER ..................................................................................................22

4.2.4 COLORIZER.......................................................................................................22

4.2.5 COLOR LOOKUP TABLE ....................................................................................25

4.3 HARDWARE CURSORS .........................................................................................26

4.3.1 INTRODUCTION.................................................................................................26

4.3.2 CURSOR PATTERNS...........................................................................................26

4.3.3 TURNING OFF 3D SUPPORT. ..............................................................................27

4.3.4 CURSOR PROCESSOR INTERNALS......................................................................28

4.3.5 ADDRESS GENERATOR .....................................................................................28

4.3.6

CURSOR BUFFER...............................................................................................28

4.3.7

CURSOR0/CURSOR1 PROCESSOR ......................................................................29

4.4 BANK SWITCHING ................................................................................................30

4.4.1 INTRODUCTION.................................................................................................30

4.4.2 HOST NOTES .....................................................................................................30

4.4.3

SEQUENCE ........................................................................................................30

OpenCores Enhanced VGA/LCD Core Datasheet 3/20/2003

www.opencores.org Rev 1.2 Preliminary

4.5 BANDWIDTH ISSUES ............................................................................................31

4.5.1 INTRODUCTION.................................................................................................31

4.5.2 CALCULATIONS ................................................................................................31

4.5.3 EXAMPLES ........................................................................................................32

ARCHITECTURE .....................................................................................................33

5.1 COLOR LOOKUP TABLE .......................................................................................33

5.2 CURSOR BASE REGISTERS ...................................................................................34

5.2 CURSOR BUFFERS ................................................................................................34

5.3 CURSOR PROCESSOR ...........................................................................................34

5.4 COLOR PROCESSOR .............................................................................................34

5.5 LINE FIFO...........................................................................................................34

5.6 VIDEO MEMORY BASE REGISTERS ......................................................................34

5.7 VIDEO TIMING GENERATOR ................................................................................34

5.8 WISHBONE MASTER INTERFACE..........................................................................35

5.9 WISHBONE SLAVE INTERFACE.............................................................................35

VGA MODES .............................................................................................................36

A.1 VERTICAL TIMING INFORMATION COMMON VGA MODES .................................36

A.2 HORIZONTAL TIMING INFORMATION COMMON VGA MODES ............................36

TARGET DEPENDENT IMPLEMENTATIONS..................................................37

CORE STRUCTURE.................................................................................................38

DESIGN NOTES........................................................................................................39

D.1 INTRODUCTION ...................................................................................................39

D.2 VGA_CURPROC....................................................................................................40