没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

Advanced RISC Machines

ARM

Document Number: ARM DDI 0027D

Issued: Dec 1994

Copyright Advanced RISC Machines Ltd (ARM) 1994

All rights reserved

ARM7DI

Data Sheet

Proprietary Notice

ARM, the ARM Powered logo, BlackICE and ICEbreaker are trademarks of Advanced RISC

Machines Ltd.

Neither the whole nor any part of the information contained in, or the product described in, this

datasheet may be adapted or reproduced in any material form except with the prior written

permission of the copyright holder.

The product described in this datasheet is subject to continuous developments and

improvements. All particulars of the product and its use contained in this datasheet are given by

ARM in good faith. However, all warranties implied or expressed, including but not limited to

implied warranties or merchantability, or fitness for purpose, are excluded.

This datasheet is intended only to assist the reader in the use of the product. ARM Ltd shall not

be liable for any loss or damage arising from the use of any information in this datasheet, or any

error or omission in such information, or any incorrect use of the product.

Change Log

Issue Date By Change

A July 1994 EH Created.

B Aug 94 BJH Updated Instruction Cycle Operations

C Oct 94 EH Sources repaired: no material changes to text

D Dec 94 PB Edited.

Preface

iv ARM7DI Data Sheet

The ARM7DI is a low-power, general purpose 32-bit RISC microprocessor with integrated debug support.

It comprises the ARM7D CPU core, and ICEbreaker module and a TAP controller. Its simple, elegant and

fully static design is particularly suitable for cost and power sensitive applications.

Enhancements

The ARM7DI is similar to the ARM6 but with the following enhancements:

■

advanced debug (integrated ICE) support for faster time to market

■

fabrication on a sub-micron process for increased speed and reduced power consumption

■

3V operation, for very low power consumption, as well as 5V operation for system compatibility

■

higher clock speedfor faster program execution.

Applications

The ARM7DI is ideally suited to those applications requiring RISC performance from a compact,

power-efficient processor. These include:

Telecomms GSM terminal controller

Datacomms Protocol conversion

Portable Computing Palmtop computer

Portable InstrumentS Handheld data acquisition unit

Automotive Engine management unit

Information Systems Smart cards

Imaging JPEG controller

Feature Summary

■

32-bit RISC processor (32-bit data & address bus)

■

Advanced debug

fully integrated ICE

■

Big and Little Endian operating modes

■

High performance RISC

■

Low power consumption

■

Fully static operation

ideal for power-sensitive applications

■

Fast interrupt response

for real-time applications

■

Virtual Memory System Support

■

Excellent high-level language support

■

Simple but powerful instruction set

Instruction

Decoder

&

Logic

Control

Address Register

Address

Incrementer

Register Bank

Barrel

Shifter

32 bit ALU

Write Data Register

Instruction

Pipeline &

Read Data

Register

Booth’s

Multiplier

D

e

b

u

g

ICEbreaker

TAP controller

i

Table of Contents

1.0 Introduction 5

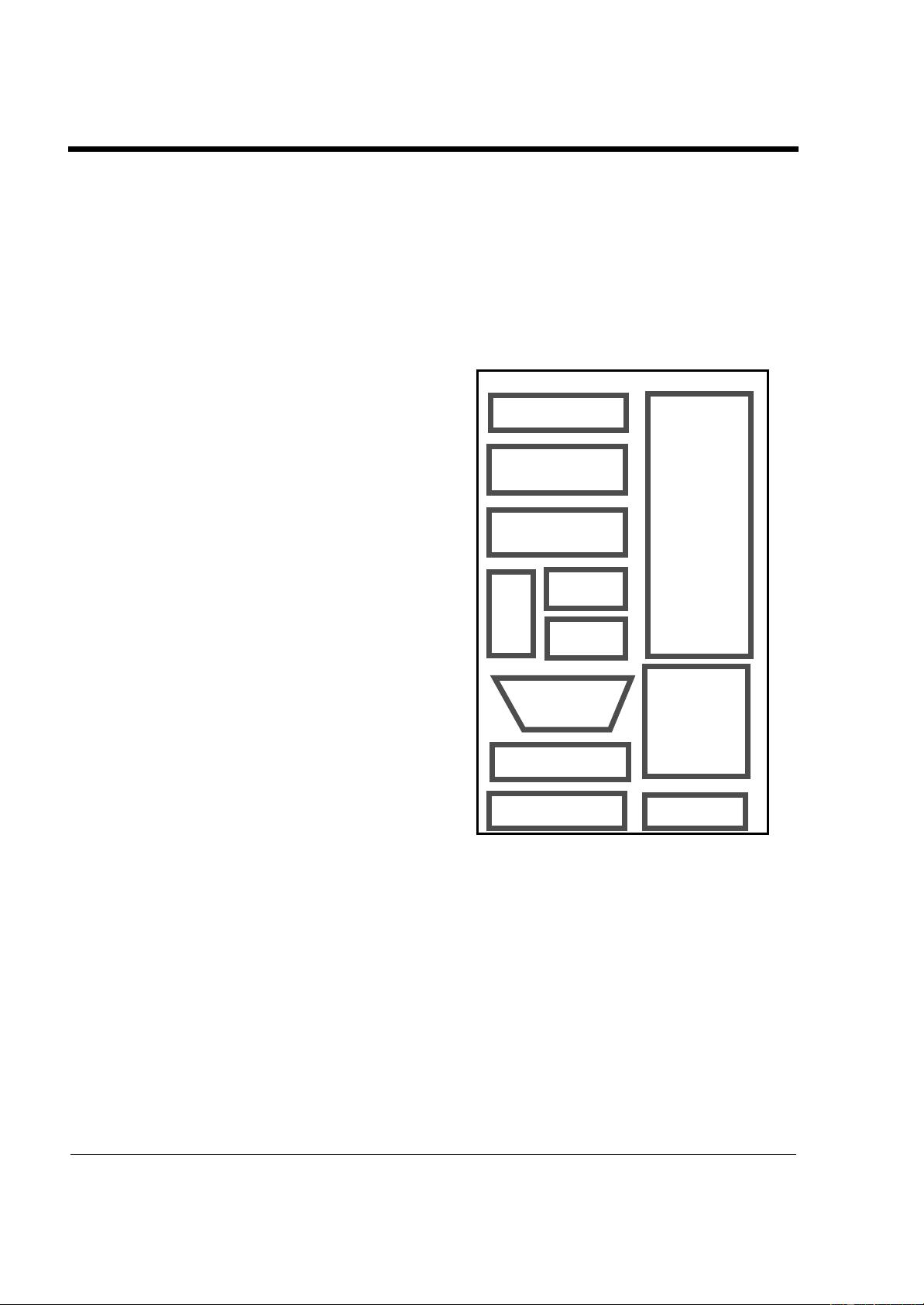

1.1 ARM7DI Block Diagram 6

1.2 ARM7D Core Diagram 7

1.3 ARM7DI Functional Diagram 8

2.0 Signal Description 9

3.0 Programmer's Model 15

3.1 Hardware Configuration Signals 15

3.2 Operating Mode Selection 16

3.3 Registers 17

3.4 Exceptions 20

3.5 Reset 24

4.0 Instruction Set 25

4.1 Instruction Set Summary 25

4.2 The Condition Field 26

4.3 Branch and Branch with link (B, BL) 27

4.4 Data processing 29

4.5 PSR Transfer (MRS, MSR) 36

4.6 Multiply and Multiply-Accumulate (MUL, MLA) 40

4.7 Single data transfer (LDR, STR) 42

4.8 Block Data Transfer (LDM, STM) 48

4.9 Single data swap (SWP) 55

4.10 Software interrupt (SWI) 57

4.11 Coprocessor data operations (CDP) 59

4.12 Coprocessor data transfers (LDC, STC) 61

4.13 Coprocessor register transfers (MRC, MCR) 64

4.14 Undefined instruction 66

4.15 Instruction Set Examples 67

5.0 Memory Interface 71

5.1 Cycle types 71

5.2 Byte addressing 72

5.3 Address timing 74

5.4 Memory management 74

5.5 Locked operations 75

5.6 Stretching access times 75

5.7 The External Data Bus 76

6.0 Coprocessor Interface 81

6.1 Interface signals 81

6.2 Data transfer cycles 82

6.3 Register transfer cycle 82

6.4 Privileged instructions 82

6.5 Idempotency 83

6.6 Undefined instructions 83

7.0 Debug Interface 85

7.1 Overview 85

7.2 Debug Systems 85

7.3 Debug Interface Signals 86

ARM7DI Data Sheet

ii

7.4 Scan Chains and JTAG Interface 89

7.5 Reset 91

7.6 Pullup Resistors 91

7.7 Instruction Register 92

7.8 Public Instructions 92

7.9 Test Data Registers 94

7.10 ARM7DI Core Clocks 99

7.11 Determining the Core and System State 100

7.12 The PC's Behaviour During Debug 103

7.13 Priorities / Exceptions 105

7.14 Scan Interface Signals 106

8.0 The ARM7DI ICEBreaker Module 109

8.1 The Watchpoint Registers 110

8.2 The Debug Control Register 115

8.3 Debug Status Register 116

8.4 Coupling Breakpoints and Watchpoints 119

8.5 Disabling ICEbreaker 120

8.6 ICEbreaker Timing 120

8.7 ICEBreaker Programming Restriction 120

9.0 Instruction Cycle Operations 121

9.1 Branch and branch with link 121

9.2 Data Operations 121

9.3 Multiply and multiply accumulate 123

9.4 Load register 123

9.5 Store register 124

9.6 Load multiple registers 125

9.7 Store multiple registers 127

9.8 Data swap 127

9.9 Software interrupt and exception entry 128

9.10 Coprocessor data operation 129

9.11 Coprocessor data transfer (from memory to coprocessor) 129

9.12 Coprocessor data transfer (from coprocessor to memory) 131

9.13 Coprocessor register transfer (Load from coprocessor) 132

9.14 Coprocessor register transfer (Store to coprocessor) 132

9.15 Undefined instructions and coprocessor absent 133

9.16 Unexecuted instructions 134

9.17 Instruction Speed Summary 134

10.0 DC Parameters 137

10.1 Absolute Maximum Ratings 137

10.2 DC Operating Conditions: 137

11.0 AC Parameters 139

12.0 Appendix - Backward Compatibility 149

Introduction

5

1.0 Introduction

The ARM7DI is part of the Advanced RISC Machines (ARM) family of general purpose 32-bit

microprocessors, which offer very low power consumption and price for high performance devices. The

architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and

related decode mechanism are much simpler in comparison with microprogrammed Complex Instruction

Set Computers. This results in a high instruction throughput and impressive real-time interrupt response

from a small and cost-effective chip.

The instruction set comprises eleven basic instruction types:

• Two of these make use of the on-chip arithmetic logic unit, barrel shifter and multiplier to perform

high-speed operations on the data in a bank of 31 registers, each 32 bits wide;

• Three classes of instruction control data transfer between memory and the registers, one optimised

for flexibility of addressing, another for rapid context switching and the third for swapping data;

• Three instructions control the flow and privilege level of execution; and

• Three types are dedicated to the control of external coprocessors which allow the functionality of

the instruction set to be extended off-chip in an open and uniform way.

The ARM instruction set is a good target for compilers of many different high-level languages. Where

required for critical code segments, assembly code programming is also straightforward, unlike some RISC

processors which depend on sophisticated compiler technology to manage complicated instruction

interdependencies.

Pipelining is employed so that all parts of the processing and memory systems can operate continuously.

Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is

being fetched from memory.

The memory interface has been designed to allow the performance potential to be realised without

incurring high costs in the memory system. Speed critical control signals are pipelined to allow system

control functions to be implemented in standard low-power logic, and these control signals facilitate the

exploitation of the fast local access modes offered by industry standard dynamic RAMs.

ARM7DI has a 32 bit address bus. All ARM processors share the same instruction set, and ARM7DI can be

configured to use a 26 bit address bus for backwards compatibility with earlier processors.

ARM7DI is a fully static CMOS implementation of the ARM which allows the clock to be stopped in any

part of the cycle with extremely low residual power consumption and no loss of state.

Notation:

0x - marks a Hexadecimal quantity

BOLD - external signals are shown in bold capital letters

binary - where it is not clear that a quantity is binary it is followed by the word binary

剩余149页未读,继续阅读

资源评论

kkkfly999

- 粉丝: 0

- 资源: 15

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功