没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

PCI Local Bus Specification

Revision 3.0

February 3, 2004

PCI LOCAL BUS SPECIFICATION, REV. 3.0

2

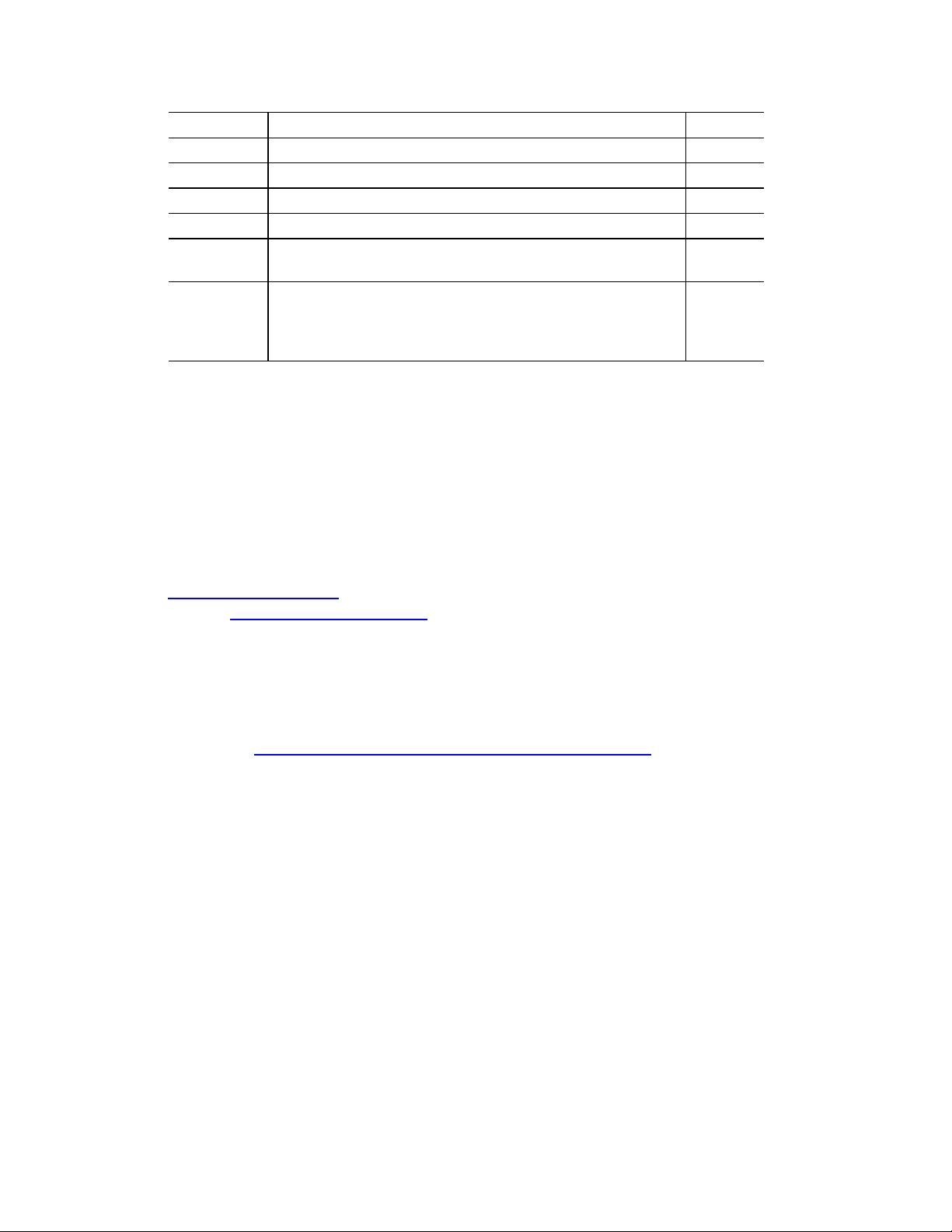

REVISION REVISION HISTORY DATE

1.0 Original issue. 6/22/92

2.0 Incorporated connector and add-in card specification. 4/30/93

2.1 Incorporated clarifications and added 66 MHz chapter. 6/1/95

2.2 Incorporated ECNs and improved readability. 12/18/98

2.3

Incorporated ECNs, errata, and deleted 5 volt only keyed

add-in cards.

3/29/02

3.0

Incorporated ECNs, errata, and removed support for the

5.0 volt keyed system board connector. Moved the

Expansion ROM description to the PCI Firmware

Specification.

2/3/04

PCI-SIG disclaims all warranties and liability for the use of this document and the

information contained herein and assumes no responsibility for any errors that may appear

in this document, nor does PCI-SIG make a commitment to update the information

contained herein.

Contact the PCI-SIG office to obtain the latest revision of the specification.

Questions regarding this PCI Local Bus Specification or membership in PCI-SIG may be

forwarded to:

Membership Services

http://www.pcisig.com

E-mail: administration@pcisig.com

Phone: 503-291-2569

Fax: 503-297-1090

Technical Support

Technical Support for this specification is available to members. For information,

please visit: http://www.pcisig.com/developers/technical_support.

DISCLAIMER

This PCI Local Bus Specification is provided “as is” with no warranties whatsoever,

including any warranty of merchantability, noninfringement, fitness for any particular

purpose, or any warranty otherwise arising out of any proposal, specification, or

sample. PCI-SIG disclaims all liability for infringement of proprietary rights, relating

to use of information in this specification. No license, express or implied, by

estoppel or otherwise, to any intellectual property rights is granted herein.

PCI Express and PCI-SIG are trademarks of PCI-SIG.

All other product names are trademarks, registered trademarks, or servicemarks of their

respective owners.

Copyright © 1992, 1993, 1995, 1998, and 2004 PCI-SIG

PCI LOCAL BUS SPECIFICATION, REV. 3.0

3

Contents

PREFACE ........................................................................................................................ 13

S

PECIFICATION

............................................................................................................... 13

I

NCORPORATION OF

E

NGINEERING

C

HANGE

N

OTICES

(ECN

S

)....................................... 13

D

OCUMENT

C

ONVENTIONS

............................................................................................ 14

1. INTRODUCTION................................................................................................... 15

1.1. S

PECIFICATION

C

ONTENTS

................................................................................. 15

1.2. M

OTIVATION

...................................................................................................... 15

1.3. PCI L

OCAL

B

US

A

PPLICATIONS

......................................................................... 16

1.4. PCI L

OCAL

B

US

O

VERVIEW

............................................................................... 17

1.5. PCI L

OCAL

B

US

F

EATURES AND

B

ENEFITS

........................................................ 18

1.6. A

DMINISTRATION

............................................................................................... 20

2. SIGNAL DEFINITION .......................................................................................... 21

2.1. S

IGNAL

T

YPE

D

EFINITION

.................................................................................. 22

2.2. P

IN

F

UNCTIONAL

G

ROUPS

.................................................................................. 22

2.2.1. System Pins................................................................................................ 23

2.2.2. Address and Data Pins.............................................................................. 24

2.2.3. Interface Control Pins............................................................................... 25

2.2.4. Arbitration Pins (Bus Masters Only) ........................................................ 27

2.2.5. Error Reporting Pins................................................................................. 27

2.2.6. Interrupt Pins (Optional) .......................................................................... 28

2.2.7. Additional Signals ..................................................................................... 31

2.2.8. 64-Bit Bus Extension Pins (Optional) ....................................................... 33

2.2.9. JTAG/Boundary Scan Pins (Optional)...................................................... 34

2.2.10. System Management Bus Interface Pins (Optional) ................................. 35

2.3. S

IDEBAND

S

IGNALS

............................................................................................ 36

2.4. C

ENTRAL

R

ESOURCE

F

UNCTIONS

....................................................................... 36

3. BUS OPERATION.................................................................................................. 37

3.1. B

US

C

OMMANDS

................................................................................................ 37

3.1.1. Command Definition ................................................................................. 37

3.1.2. Command Usage Rules ............................................................................. 39

3.2. PCI P

ROTOCOL

F

UNDAMENTALS

....................................................................... 42

3.2.1. Basic Transfer Control.............................................................................. 43

3.2.2. Addressing................................................................................................. 44

3.2.3. Byte Lane and Byte Enable Usage ............................................................ 56

3.2.4. Bus Driving and Turnaround .................................................................... 57

3.2.5. Transaction Ordering and Posting ........................................................... 58

3.2.6. Combining, Merging, and Collapsing....................................................... 62

PCI LOCAL BUS SPECIFICATION, REV. 3.0

4

3.3. B

US

T

RANSACTIONS

........................................................................................... 64

3.3.1. Read Transaction ...................................................................................... 65

3.3.2. Write Transaction...................................................................................... 66

3.3.3. Transaction Termination........................................................................... 67

3.4. A

RBITRATION

..................................................................................................... 87

3.4.1. Arbitration Signaling Protocol.................................................................. 89

3.4.2. Fast Back-to-Back Transactions ............................................................... 91

3.4.3. Arbitration Parking................................................................................... 94

3.5. L

ATENCY

............................................................................................................ 95

3.5.1. Target Latency........................................................................................... 95

3.5.2. Master Data Latency................................................................................. 98

3.5.3. Memory Write Maximum Completion Time Limit.....................................99

3.5.4. Arbitration Latency ................................................................................. 100

3.6. O

THER

B

US

O

PERATIONS

................................................................................. 110

3.6.1. Device Selection ...................................................................................... 110

3.6.2. Special Cycle ........................................................................................... 111

3.6.3. IDSEL Stepping....................................................................................... 113

3.6.4. Interrupt Acknowledge ............................................................................ 114

3.7. E

RROR

F

UNCTIONS

........................................................................................... 115

3.7.1. Parity Generation.................................................................................... 115

3.7.2. Parity Checking....................................................................................... 116

3.7.3. Address Parity Errors ............................................................................. 116

3.7.4. Error Reporting....................................................................................... 117

3.7.5. Delayed Transactions and Data Parity Errors ....................................... 120

3.7.6. Error Recovery........................................................................................ 121

3.8. 64-B

IT

B

US

E

XTENSION

................................................................................... 123

3.8.1. Determining Bus Width During System Initialization............................. 126

3.9. 64-

BIT

A

DDRESSING

......................................................................................... 127

3.10. S

PECIAL

D

ESIGN

C

ONSIDERATIONS

.............................................................. 130

4. ELECTRICAL SPECIFICATION...................................................................... 137

4.1. O

VERVIEW

....................................................................................................... 137

4.1.1. Transition Road Map .............................................................................. 137

4.1.2. Dynamic vs. Static Drive Specification ................................................... 138

4.2. C

OMPONENT

S

PECIFICATION

............................................................................ 139

4.2.1. 5V Signaling Environment ...................................................................... 140

4.2.2. 3.3V Signaling Environment ................................................................... 146

4.2.3. Timing Specification................................................................................ 150

4.2.4. Indeterminate Inputs and Metastability .................................................. 155

4.2.5. Vendor Provided Specification................................................................ 156

4.2.6. Pinout Recommendation ......................................................................... 157

PCI LOCAL BUS SPECIFICATION, REV. 3.0

5

4.3. S

YSTEM

B

OARD

S

PECIFICATION

....................................................................... 158

4.3.1. Clock Skew .............................................................................................. 158

4.3.2. Reset ........................................................................................................ 158

4.3.3. Pull-ups ................................................................................................... 161

4.3.4. Power ...................................................................................................... 163

4.3.5. System Timing Budget ............................................................................. 164

4.3.6. Physical Requirements ............................................................................ 167

4.3.7. Connector Pin Assignments .................................................................... 168

4.4. A

DD

-

IN

C

ARD

S

PECIFICATION

.......................................................................... 171

4.4.1. Add-in Card Pin Assignment................................................................... 171

4.4.2. Power Requirements ............................................................................... 176

4.4.3. Physical Requirements ............................................................................ 178

5. MECHANICAL SPECIFICATION.................................................................... 181

5.1. O

VERVIEW

....................................................................................................... 181

5.2. A

DD

-

IN

C

ARD

P

HYSICAL

D

IMENSIONS AND

T

OLERANCES

............................... 182

5.3. C

ONNECTOR

P

HYSICAL

D

ESCRIPTION

.............................................................. 195

5.4. C

ONNECTOR

P

HYSICAL

R

EQUIREMENTS

.......................................................... 205

5.5. C

ONNECTOR

P

ERFORMANCE

S

PECIFICATION

.................................................... 206

5.6. S

YSTEM

B

OARD

I

MPLEMENTATION

.................................................................. 207

6. CONFIGURATION SPACE .................................................................................. 213

6.1. C

ONFIGURATION

S

PACE

O

RGANIZATION

.......................................................... 213

6.2. C

ONFIGURATION

S

PACE

F

UNCTIONS

................................................................ 216

6.2.1. Device Identification ............................................................................... 216

6.2.2. Device Control ........................................................................................ 217

6.2.3. Device Status ........................................................................................... 219

6.2.4. Miscellaneous Registers.......................................................................... 221

6.2.5. Base Addresses........................................................................................ 224

6.3. PCI E

XPANSION

ROM

S

................................................................................... 228

6.4. V

ITAL

P

RODUCT

D

ATA

..................................................................................... 229

6.5. D

EVICE

D

RIVERS

.............................................................................................. 229

6.6. S

YSTEM

R

ESET

................................................................................................. 230

6.7. C

APABILITIES

L

IST

........................................................................................... 230

6.8. M

ESSAGE

S

IGNALED

I

NTERRUPTS

.................................................................... 231

6.8.1. MSI Capability Structure ........................................................................ 232

6.8.2. MSI-X Capability and Table Structures .................................................. 238

6.8.3. MSI and MSI-X Operation ...................................................................... 246

7. 66 MHZ PCI SPECIFICATION.......................................................................... 255

7.1. I

NTRODUCTION

................................................................................................. 255

7.2. S

COPE

............................................................................................................... 255

7.3. D

EVICE

I

MPLEMENTATION

C

ONSIDERATIONS

.................................................. 255

7.3.1. Configuration Space................................................................................ 255

7.4. A

GENT

A

RCHITECTURE

.................................................................................... 256

剩余343页未读,继续阅读

资源评论

weixin_397793952017-12-11PCI必备必备

weixin_397793952017-12-11PCI必备必备 vgezi2021-09-13这么高的积分下载,简直就是抢劫啊

vgezi2021-09-13这么高的积分下载,简直就是抢劫啊 tjdyx2017-06-26学习PCI 必备

tjdyx2017-06-26学习PCI 必备 chendaohong2017-06-06查到了我要的东西,很有用

chendaohong2017-06-06查到了我要的东西,很有用

jianjunzaixian

- 粉丝: 1

- 资源: 12

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功