没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet of

Avnet, Inc.

Engineering Services

Copyright 2006

AES-SP3-PCIE-SCH 2.1

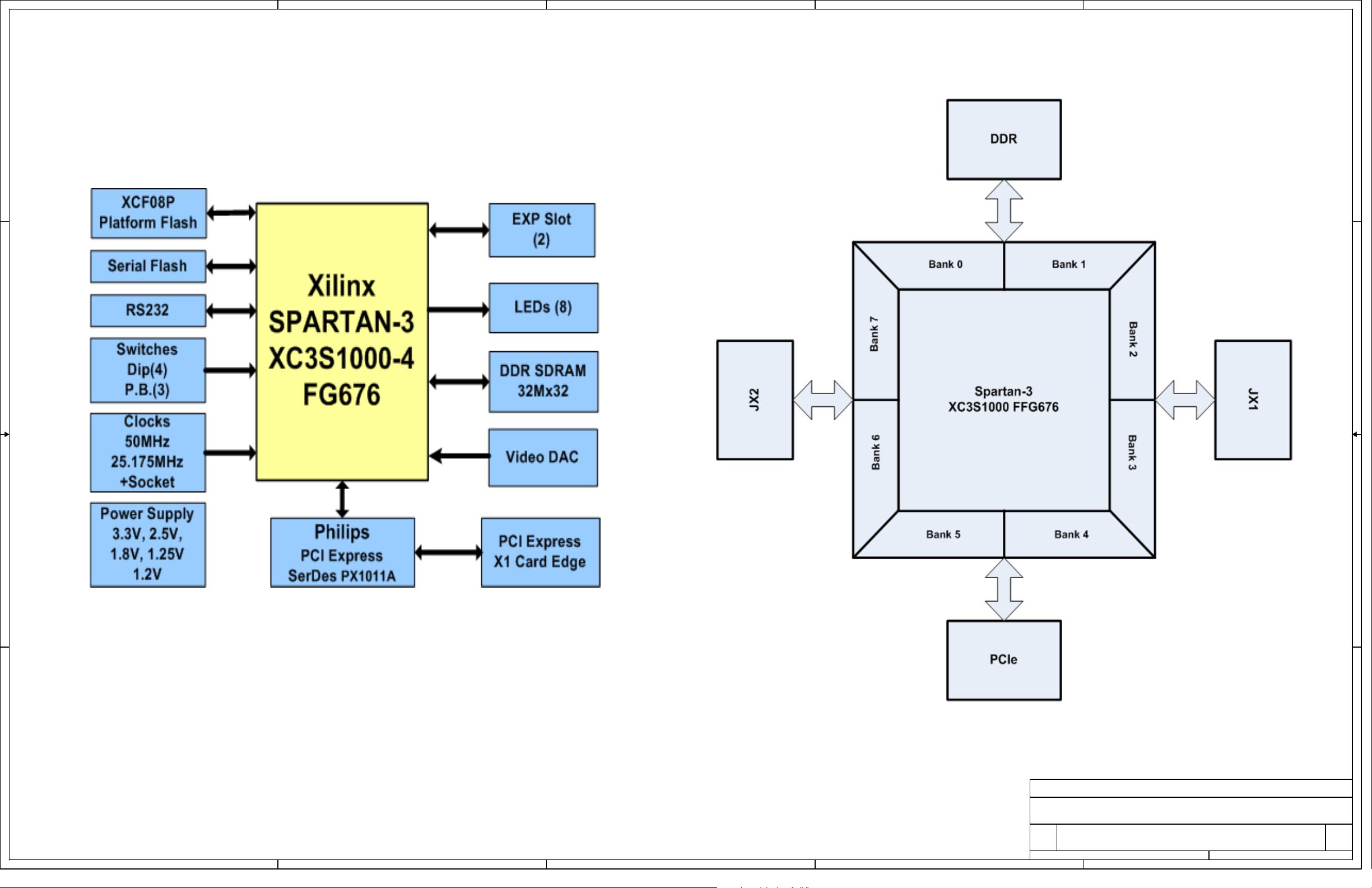

Spartan-3 PCIe Starter Board

B

1Thursday, May 03, 2007 13

Cover sheet

Title

Size Document Number Rev

Date: Sheet of

Avnet, Inc.

Engineering Services

Copyright 2006

AES-SP3-PCIE-SCH 2.1

Spartan-3 PCIe Starter Board

B

1Thursday, May 03, 2007 13

Cover sheet

Title

Size Document Number Rev

Date: Sheet of

Avnet, Inc.

Engineering Services

Copyright 2006

AES-SP3-PCIE-SCH 2.1

Spartan-3 PCIe Starter Board

B

1Thursday, May 03, 2007 13

Cover sheet

05/03/07

FPGA Power

Function

12

www.em.avnet.com/xilinx

1

Cover Sheet

6

4

FPGA - PCIe Banks 6 & 7

10

8

Board Power

Sheet Number

5

3FPGA - Banks 0 & 1

Avnet Engineering Services

11

7

9

FPGA Configuration

Copyright 2006, Avnet, Inc. All Rights Reserved.

This material may not be reproduced, distributed, republished, displayed, posted, transmitted or copied in

any form or by any means without the prior written permission of Avnet, Inc. AVNET and the AV logo are

registered trademarks of Avnet, Inc. All trademarks and trade names are the properties of their respective

owners and Avnet, Inc. disclaims any proprietary interest or right in trademarks, service marks and trade

names other than its own.

Avnet is not responsible for typographical or other errors or omissions or for direct, indirect, incidental or

consequential damages related to this material or resulting from its use. Avnet makes no warranty or

representation respecting this material, which is provided on an "AS IS" basis. AVNET HEREBY

DISCLAIMS ALL WARRANTIES OR LIABILITY OF ANY KIND WITH RESPECT THERETO, INCLUDING,

WITHOUT LIMITATION, REPRESENTATIONS REGARDING ACCURACY AND COMPLETENESS, ALL

IMPLIED WARRANTIES AND CONDITIONS OF MERCHANTABILITY, SUITABILITY OR FITNESS FOR A

PARTICULAR PURPOSE, TITLE AND/OR NON-INFRINGEMENT. This material is not designed, intended

or authorized for use in medical, life support, life sustaining or nuclear applications or applications in which

the failure of the product could result in personal injury, death or property damage. Any party using or

selling products for use in any such applications do so at their sole risk and agree that Avnet is not liable,

in whole or in part, for any claim or damage arising from such use, and agree to fully indemnify, defend and

hold harmless Avnet from and against any and all claims, damages, loss, cost, expense or liability arising

out of or in connection with the use or performance of products in such applications.

Spartan-3 PCIe Starter Board

REVISION 2.1

FPGA - Banks 2 & 3

FPGA - LVDS Banks 4 & 5

PCI Express

DDR SDRAM

Video DAC

2Block Diagram

13

Revision Notes

Powered By:

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet of

Avnet, Inc.

Engineering Services

Copyright 2006

AES-SP3-PCIE-SCH 2.1

Spartan-3 PCIe Starter Board

B

2Thursday, May 03, 2007 13

Block Diagram

Title

Size Document Number Rev

Date: Sheet of

Avnet, Inc.

Engineering Services

Copyright 2006

AES-SP3-PCIE-SCH 2.1

Spartan-3 PCIe Starter Board

B

2Thursday, May 03, 2007 13

Block Diagram

Title

Size Document Number Rev

Date: Sheet of

Avnet, Inc.

Engineering Services

Copyright 2006

AES-SP3-PCIE-SCH 2.1

Spartan-3 PCIe Starter Board

B

2Thursday, May 03, 2007 13

Block Diagram

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

A2

DDR_A0

DDR_A1

DDR_A2

DDR_A3 A3

A10

A11

A8

A9

BA0

BA1

A12

RAS#

CAS#

CS#

WE#

CKE

CK0#

CK0

A0

A1

DDR_D16

DDR_D8

DDR_D9

DDR_D10

DDR_D11

DDR_D12

DDR_D13

DDR_D14

DDR_D15

DDR_D0

DDR_D1

DDR_D2

DDR_D3

DDR_D4

DDR_D5

DDR_D6

DDR_D7

DDR_D17

DM0

DDR_D18

DDR_D19

DM1

DDR_D20

DDR_D21

DDR_D22

DDR_D23

DM2

DM3

CK1#

DDR_D24

DDR_D25

DDR_D26

DDR_D27

DDR_D28

DDR_D29

DDR_D30

DDR_D31

CK1

SW1

SW4

SW3

SW2

LED1

LED7

LED8

LED2

LED3

LED5

LED6

DDR_D26

DDR_D27

DDR_D28

DDR_D29

DDR_D30

DDR_D31

WE#

A13

A0

BA0

A1

BA1

CS#

A2

A3

A4

A5

A6

A7

RAS#

A8

A9

A10

A11

CAS#

A12

CKE

LED5

LED6

LED7

LED8

DM2

DM3

CK1#

CK1

Cntrl0_Rst_DQS_Div_Out

DDR_D24

DDR_D25

SW1

CK0#

CK0

DM0

SW2

SW3

DM1

DDR_D9

DDR_D10

DDR_D11

DDR_D12

DDR_D13

DDR_D14

DDR_D15

DDR_D1

DDR_D2

DDR_D3

DDR_D4

DDR_D5

DDR_D6

DDR_D7

DDR_D16

DDR_D0

DDR_D17

DDR_D8

DDR_D18

DDR_D19

DDR_D20

DDR_D21

DDR_D22

DDR_D23

LED1

LED2

Cntrl0_Rst_DQS_Div_In

A6

A7

A4

A5

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13 A13

SW4

LED3

+3.3V

+3.3V

+3.3V

+2.5V

+2.5V

+2.5V

+2.5V

+2.5V

+1.25V_REF+1.25V_REF

+2.5V

+2.5V

+2.5V

+1.25V_TT

NC_NET4,5,6

NC_NET4,5,6

NC_NET4,5,6

NC_NET4,5,6

NC_NET4,5,6

NC_NET4,5,6

NC_NET4,5,6

NC_NET4,5,6

NC_NET4,5,6

NC_NET4,5,6

NC_NET4,5,6

NC_NET4,5,6

NC_NET 4,5,6

NC_NET 4,5,6

NC_NET 4,5,6

NC_NET 4,5,6

NC_NET 4,5,6

NC_NET 4,5,6

NC_NET 4,5,6

NC_NET 4,5,6

NC_NET 4,5,6

NC_NET 4,5,6

DDR_DM310

DDR_A[0:13]10

DDR_CKE10

DDR_CK010

DDR_CK0#10

DDR_CS#10

DDR_WE#10

DDR_RAS#10

DDR_CAS#10

DDR_BA010

DDR_BA110

DDR_D[0:31]10

DDR_CK110

DDR_CK1#10

DDR_DM010

DDR_DM110

DDR_DM210

DDR_DQS310

DDR_DQS010

DDR_DQS110

DDR_CK_FB 5

DDR_DQS210

JX1_SE_CLK_IN6

LED44

Title

Size Document Number Rev

Date: Sheet of

Avnet, Inc.

Engineering Services

Copyright 2006

AES-SP3-PCIE-SCH 2.1

Spartan-3 PCIe Starter Board

C

3Thursday, May 03, 2007 13

FPGA Banks 0 & 1

Title

Size Document Number Rev

Date: Sheet of

Avnet, Inc.

Engineering Services

Copyright 2006

AES-SP3-PCIE-SCH 2.1

Spartan-3 PCIe Starter Board

C

3Thursday, May 03, 2007 13

FPGA Banks 0 & 1

Title

Size Document Number Rev

Date: Sheet of

Avnet, Inc.

Engineering Services

Copyright 2006

AES-SP3-PCIE-SCH 2.1

Spartan-3 PCIe Starter Board

C

3Thursday, May 03, 2007 13

FPGA Banks 0 & 1

Place R25 close to U18.C10.

Total length of U18.C10 to

R25 to U18.D10 is 2X the

routed DDR Clock length

(DDR_CK0, DDR_CK1).

R11

1K

R11

1K

R31 33R0R31 33R0

R4 100R4 100

C4

0.1uF

C4

0.1uF

U19

NC7SV126

U19

NC7SV126

2 4

5

1

3

SW5

SW DIP-4/SM

SW5

SW DIP-4/SM

U23

NC7SV126

U23

NC7SV126

24

5

1

3

RP11 24R0RP11 24R0

18

27

36

45

D5

LED3

D5

LED3

R28

49R9

R28

49R9

D7

LED5

D7

LED5

R7

4.75K

R7

4.75K

R67 100R67 100

R37 33R0R37 33R0

C169

0.1uF

C169

0.1uF

U12

SN74CB3T1G125

U12

SN74CB3T1G125

A

2

B

4

OE

1

GND

3

VCC

5

R23

49R9

R23

49R9

R8

1K

R8

1K

C100

0.1uF

C100

0.1uF

RP32 24R0RP32 24R0

18

27

36

45

U26

DNI

U26

DNI

VCC

4

EN

1

GND

2

OUT

3

RP27

10K

RP27

10K

1 8

2 7

3 6

4 5

D3

LED1

D3

LED1

D6

LED4

D6

LED4

R25 24R0R25 24R0

bank0

bank1

add for 1500 & 2000

add for 1500 & 2000

U18A

XC3S1000_FG676

bank0

bank1

add for 1500 & 2000

add for 1500 & 2000

U18A

XC3S1000_FG676

IO_0_No_Pair_4

C8

IO_0_No_Pair_5

C12

IO_0_No_Pair_6

E13

IO_0_No_Pair_7

H11

IO_0_No_Pair_8

H12

IO_0_No_Pair_9/VREF_0

B3

IO_0_No_Pair_10/VREF_0

F7

IO_L01N_0/VRP_0

E5

IO_L01P_0/VRN_0

D5

IO_L05N_0

B4

IO_L05P_0/VREF_0

A4

IO_L06N_0

C5

IO_L06P_0

B5

IO_L07N_0

E6

IO_L07P_0

D6

IO_L08N_0

C6

IO_L08P_0

B6

IO_L09N_0

E7

IO_L09P_0

D7

IO_L10N_0

B7

IO_L10P_0

A7

IO_L11N_0

G8

IO_L11P_0

F8

IO_L12N_0

E8

IO_L12P_0

D8

IO_L15N_0

B8

IO_L15P_0

A8

IO_L16N_0

G9

IO_L16P_0

F9

IO_L17N_0

E9

IO_L17P_0

D9

IO_L18N_0

C9

IO_L18P_0

B9

IO_L19N_0

F10

IO_L19P_0

E10

IO_L22N_0

D10

IO_L22P_0

C10

IO_L23N_0

B10

IO_L23P_0

A10

IO_L24N_0

G11

IO_L24P_0

F11

IO_L25N_0

E11

IO_L25P_0

D11

IO_L26N_0

B11

IO_L26P_0/VREF_0

A11

IO_L27N_0

G12

IO_L27P_0

H13

IO_L28N_0

F12

IO_L28P_0

E12

IO_L29N_0

B12

IO_L29P_0

A12

IO_L30N_0

G13

IO_L30P_0

F13

IO_L31N_0

D13

IO_L31P_0/VREF_0

C13

IO_L32N_0/GCLK7

B13

IO_L32P_0/GCLK6

A13

IO_1_No_Pair_0

A14

IO_1_No_Pair_1

A22

IO_1_No_Pair_2

A23

IO_1_No_Pair_3

D16

IO_1_No_Pair_4

E18

IO_1_No_Pair_5

F14

IO_1_No_Pair_8/VREF_1

C15

IO_L01N_1/VRP_1

D22

IO_L01P_1/VRN_1

E22

IO_L04N_1

B23

IO_L04P_1

C23

IO_L05N_1

E21

IO_L05P_1

F21

IO_L06N_1/VREF_1

B22

IO_L06P_1

C22

IO_L07N_1

C21

IO_L07P_1

D21

IO_L08N_1

A21

IO_L08P_1

B21

IO_L09N_1

D20

IO_L09P_1

E20

IO_L10N_1/VREF_1

A20

IO_L10P_1

B20

IO_L11N_1

E19

IO_L11P_1

F19

IO_L12N_1

C19

IO_L12P_1

D19

IO_L15N_1

A19

IO_L15P_1

B19

IO_L16N_1

F18

IO_L16P_1

G18

IO_L18N_1

B18

IO_L18P_1

C18

IO_L19N_1

F17

IO_L19P_1

G17

IO_L22N_1

D17

IO_L22P_1

E17

IO_L23N_1

A17

IO_L23P_1

B17

IO_L24N_1

G16

IO_L24P_1

H16

IO_L25N_1

E16

IO_L25P_1

F16

IO_L26N_1

A16

IO_L26P_1

B16

IO_L27N_1

G15

IO_L27P_1

H15

IO_L28N_1

E15

IO_L28P_1

F15

IO_L29N_1

A15

IO_L29P_1

B15

IO_L30N_1

G14

IO_L30P_1

H14

IO_L31N_1/VREF_1

D14

IO_L31P_1

E14

IO_L32N_1/GCLK5

B14

IO_L32P_1/GCLK4

C14

IO_0_No_Pair_11/VREF_0

G10

IO_0_No_Pair_3

C4

IO_0_No_Pair_2

A6

IO_0_No_Pair_1

A5

IO_0_No_Pair_0

A3

IO_1_No_Pair_6

F20

IO_1_No_Pair_7

G19

IO_1_No_Pair_9/VREF_1

C17

IO_1_No_Pair_10/VREF_1

D18

R38

4.75K

R38

4.75K

RP12 24R0RP12 24R0

18

27

36

45

R24

49R9

R24

49R9

D4

LED2

D4

LED2

R10

1K

R10

1K

D8

LED6

D8

LED6

D9

LED7

D9

LED7

U20

50MHz

U20

50MHz

VCC

4

EN

1

GND

2

OUT

3

D2

ERROR

D2

ERROR

R9

1K

R9

1K

R62 100R62 100

D10

LED8

D10

LED8

RP38 24R0RP38 24R0

18

27

36

45

R27

49R9

R27

49R9

R74

4.75K

R74

4.75K

R66 100R66 100

R22

49R9

R22

49R9

C1090.1uF C1090.1uF

R64 100R64 100

R73 33R0R73 33R0

C189

0.1uF

C189

0.1uF

RP7 24R0RP7 24R0

18

27

36

45

OSC

U10

OSC_8PIN

OSC

U10

OSC_8PIN

VCC

8

ENABLE

1

GND

4

OUT

5

RP43 24R0RP43 24R0

18

27

36

45

R60 100R60 100

C940.1uF C940.1uF

C1790.1uF C1790.1uF

C159 0.1uFC159 0.1uF R63 100R63 100

U40

NC7SV126

U40

NC7SV126

24

5

1

3

RP15 24R0RP15 24R0

18

27

36

45

R61 100R61 100

R35 33R0R35 33R0

RP3 24R0RP3 24R0

18

27

36

45

R65 100R65 100

SW4

FPGA Reset

SW4

FPGA Reset

3

1

4

2

剩余12页未读,继续阅读

资源评论

gshgshgsh

- 粉丝: 1

- 资源: 5

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功