Cadence IC 设计实验

实验六 NC-Verilog Simulator 实验

实验目的:NC_verilog 仿真器的使用,包括编译、运行和仿真。

预备工作:

cp /eva01/cdsmgr/ training_IC_data/NCVlog_5_0.tarZ .

tar -vxfZ NCVlog_5_0.tarZ

Lab1。运行一个简单的 Verilog 设计

[1]、设置设计环境

1.cd NCVlog_5_0/lab1-mux

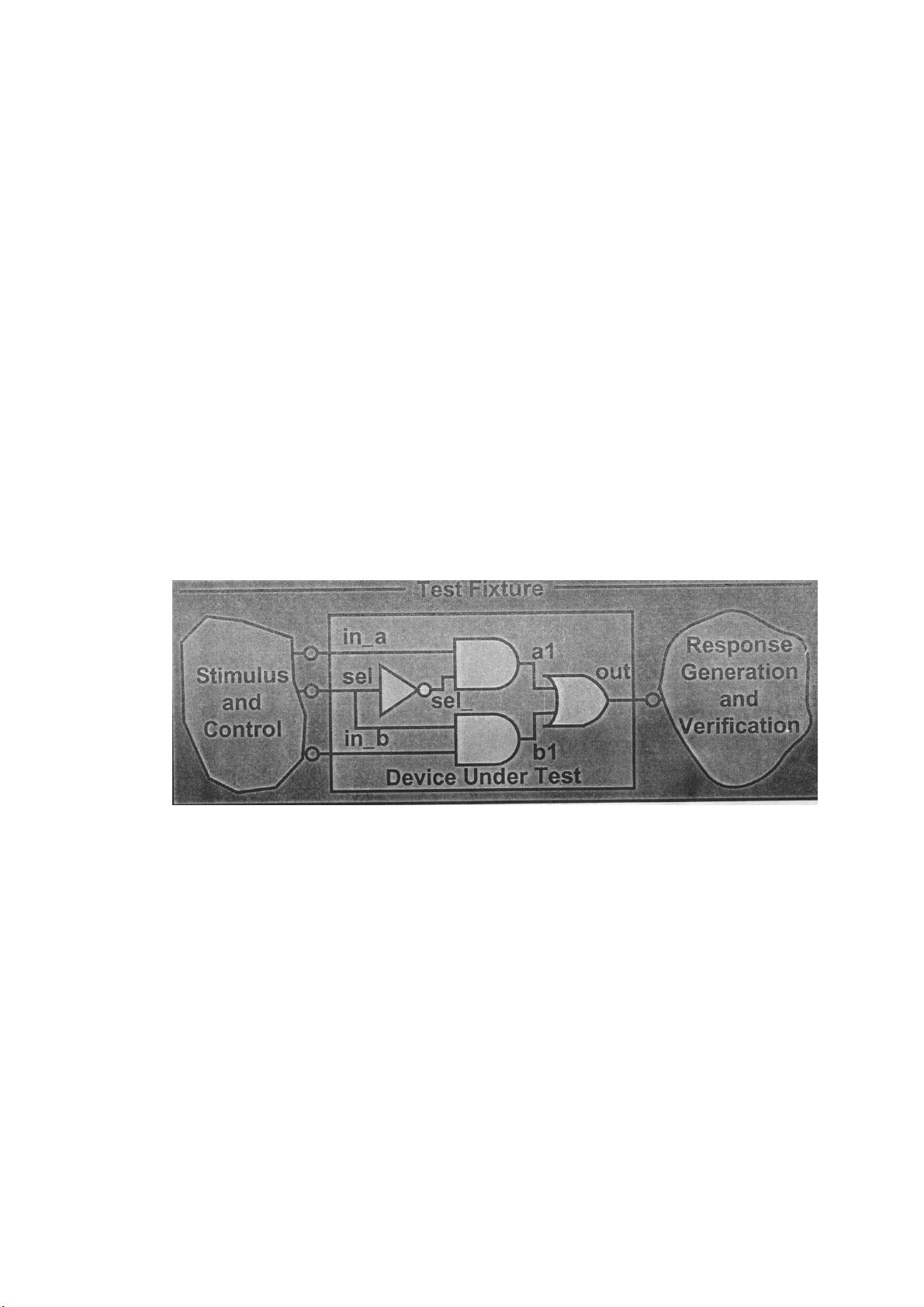

这个目录包含了用来描述一个多路选择器和其测试平台的 verilog 模块。以下是

mux_test.v 模块内功能模块的端口框图。

建议:如果有时间,你最好看一看各模块(module)的 Verilog 代码!

2.创建 cds.lib 文件,

vi cds.lib(回车)

按小写”i”切换到编辑模式,在其中写入:

Define lab1muxlib ./lab1-mux.lib

有关 vi 的编辑命令,请参阅相关资料。如”Esc”键切换到命令状态,在命令状态下,”x”

是删除当前字符,”a”是在当前光标后写入,”:wq”是存盘退出,”:!q”是不保存退出。

存盘退出

3.创建(库)文件夹(即目录):

mkdir lab1-mux.lib (回车)

4.类似步骤 1,创建 hdl.var 文件,在其中写入:

Define WORK lab1muxlib

存盘退出

5.查看 verilog 源文件。mux.v 是 2 选 1 多路选择器 MUX2_1 的门级建模源文件,mux_test.v

- 1

- 2

前往页