没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

fsm_perl: A Script to Generate RTL Code for State

Machines and Synopsys Synthesis Scripts

Clifford E. Cummings

Sunburst Design, Inc.

ABSTRACT

Coding a Verilog RTL model of a state machine requires significant effort to generate an

efficient synthesizable implementation. There are a number of different coding styles that can

yield different results with varying degrees of efficiency. Because of the effort required to code a

Verilog state machine, an engineer typically makes a guess as to which coding style will yield a

good implementation and then rarely experiments with other styles after the first model simulates

correctly.

This paper details a new and highly abbreviated language for coding a state machine and then

describes the use of a Perl script called fsm_perl to turn the abbreviated code into a variety of

synthesizable models for synthesis experimentation.

The fsm_perl also generates an accompanying dc_shell script to synthesize and compare the area

and timing of each synthesized implementation.

SNUG 1999

fsm_perl

Rev 1.1

2

1.0

Introduction

Coding a Finite State Machine (FSM) is not a difficult task but does involve a fair amount of

typing. Efficient Verilog coding styles are well known but which FSM state-encoding style will

give the best results is not obvious. The ability to easily generate different Verilog FSM designs

and the accompanying synthesis scripts was the reason fsm_perl was developed. Fsm_perl is a

freely available Perl script designed to make Finite State Machine (FSM) coding,

experimentation and synthesis easy and efficient. Instructions on how to download fsm_perl from

the Sunburst Design web site are included at the end of this paper.

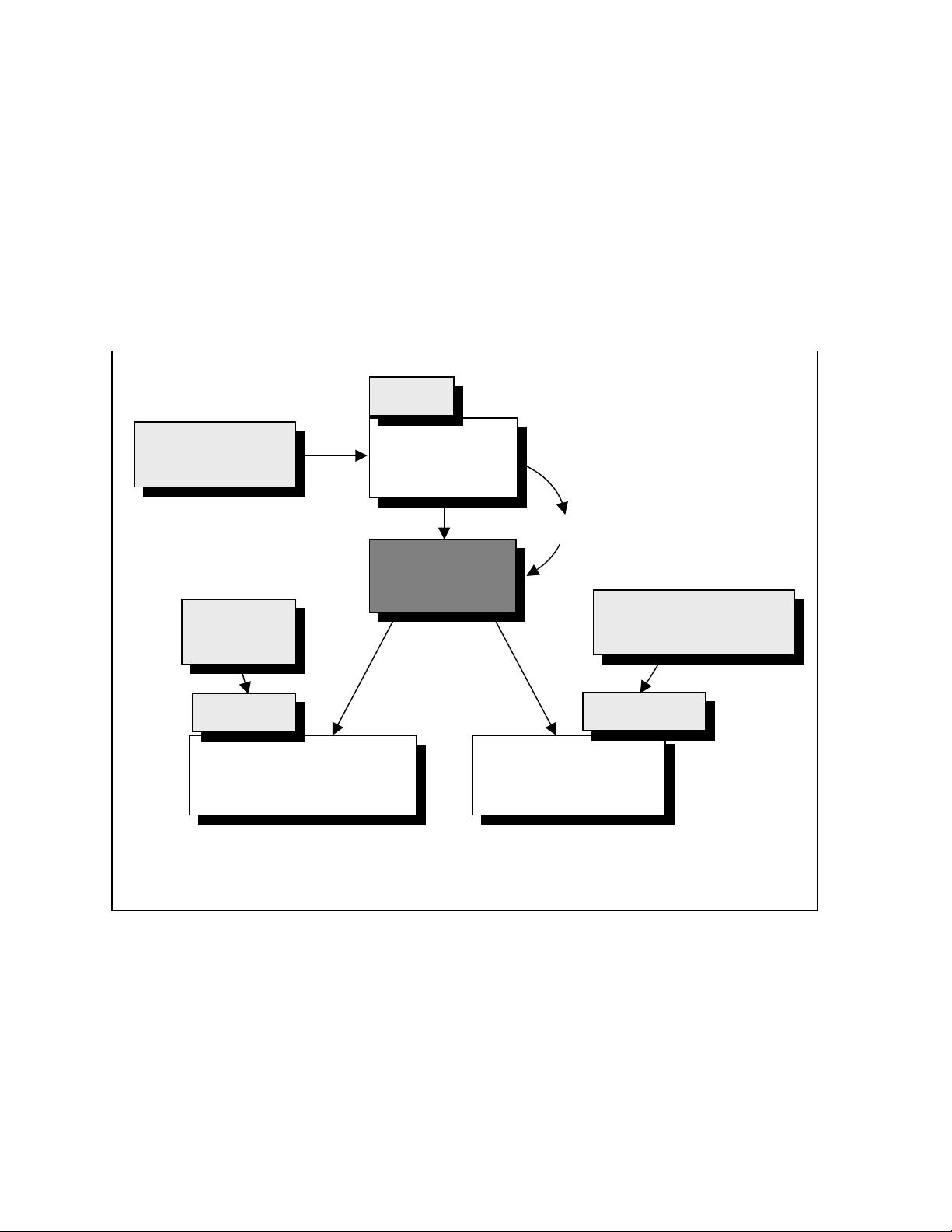

Figure 1 shows the basic fsm_perl design flow. An fsm_perl source file is coded using any text

editor, and then the source file is compiled using the fsm_perl command. Fsm_perl generates two

files, the synthesizable Verilog source code file and a Synopsys synthesis script. The Synopsys

synthesis script can then be run using dc_shell to read and compile the Verilog FSM code,

produce a Verilog gate-level netlist, produce the corresponding SDF timing file and an

area/timing report file.

Figure 1 - fsm_perl Design Flow

m

odule fsm1 (...);

...

endmodule

foreach (...) {

...

}

Verilog

FSM file

Synopsys

synthesis script

fsm_perl

script

fsm1.v

fsm1.scr

fsm_perl <options> fsm1

dc_shell -f fsm1.scr

fsm_perl

source code

IDLE :: ...

BBUSY:: ...

...

fsm1

SNUG 1999

fsm_perl

Rev 1.1

3

2.0

Basic fsm_perl Syntax

The fsm_perl syntax was designed to make FSM coding simple, compact and easily interpreted;

indeed, the fsm_perl syntax was intended to be easier to read and maintain than an equivalent

Verilog source file for the same FSM. To this end, the basic fsm_perl syntax largely revolves

around triplets to describe state diagram transition arcs.

In its most basic form, an fsm_perl source code file consists of state names, followed by one or

more triplets consisting of input statements, next state values and Mealy- or Moore-output(s)

assignments. Specifying all three fields is not required for every triplet. Legal triplet

combinations are detailed in section 5.

3.0

State Names and Encodings

Each state in the state machine must appear as a left-side argument to a state-separator operator

(a pair of adjacent colons ::). Only one adjacent colon-pair is permitted for each defined state

and no white space is permitted between the colons.

State name example:

IDLE:: ...

READ:: ...

WAIT:: ...

DONE:: ...

The first state listed will be the reset-state (the state that the state machine will go to on reset).

The state names may be optionally followed by a binary state encoding enclosed within

parentheses between the state name and the state-separator operator.

State name and encoding example:

IDLE (00):: ...

READ (01):: ...

WAIT (11):: ...

DONE (10):: ...

If user-defined state encodings are specified, then all of the states must specify a user-defined

state encoding; otherwise, fsm_perl will report a state encoding error.

4.0

Triplets

Triplets are one or more comma-separated groups consisting of input statements, next state

values and Mealy or Moore outputs assignments. Specifying all three fields is not required for

every triplet. Legal triplet combinations are detailed in section 5. Triplets must appear as a right-

side argument to a state-separator operator (::).

SNUG 1999

fsm_perl

Rev 1.1

4

5.0

Legal Triplet Statements

5.1

(Input)

The input statement is enclosed in parentheses ()'s and is an expression that is used as a Boolean

test. The code between the parentheses must be legal Verilog code since this expression will be

copied directly into the Verilog code generated by fsm_perl. At this time, fsm_perl does no

syntax checking of the Verilog expression between the parentheses; therefore, a Verilog syntax

error placed in the fsm_perl source code will be written to the generated Verilog output file and

will not be detected until the Verilog output file is compiled.

5.2

Next State

The next state statement is not enclosed in either parentheses or curly braces. The next state value

must exactly match one of the state names used in the fsm_perl source code.

5.3

{Outputs}

Output statements are one or more Mealy outputs enclosed in curly braces {}'s or one or more

Moore outputs enclosed in curly braces {}'s.

IDLE :: ...

CFG_WR :: ( nIRDY) CFG_WR {reg_we=0},

(!nIRDY) TURN_AR {reg_we=1},

{nDEVSEL=0, nTRDY=0};

TURN_AR:: ...

Figure 2 - fsm_perl Triplets

_

____

n

IRDY

/

reg_we=1

n

IRDY

/

reg_we=0

CFG_WR

nDEVSEL = 0

nTRDY = 0

I

DLE

TURN_AR

M

ealy output

Mealy output

Moore outputs

State Name

Input condition

Input condition

Triplet

(

Input ) Next

{

Outputs }

剩余19页未读,继续阅读

资源评论

drjiachen

- 粉丝: 168

- 资源: 2144

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功