没有合适的资源?快使用搜索试试~ 我知道了~

Virtex-5器件一览(中文)

需积分: 10 10 下载量 190 浏览量

2013-06-18

16:02:00

上传

评论

收藏 284KB PDF 举报

温馨提示

试读

11页

Virtex-5的相关器件描述,对相关器件进行了罗列与介绍,以及使用方法等。

资源推荐

资源详情

资源评论

DS100 (v3.0) 2007 年 2 月 2 日 www.xilinx.com/cn

先期产品技术说明 1

© 2006 - 2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

PowerPC is a trademark of IBM, Inc. All other trademarks are the property of their respective owners. All specifications are subject to change without notice.

概述

Virtex™-5 系列提供 FPGA 市场中最新最强大的功能。Virtex-5 系列采用第二代 ASMBL™(高级硅片组合模块)列式架构,

包含四种截然不同的平台 (子系列),比此前任何 FPGA 系列提供的选择范围都大。每种平台都包含不同的功能配比,以满

足诸多高级逻辑设计的需求。本概述包含关于 LX、LXT 和 SXT 平台的详细信息。除了最先进的高性能逻辑架构,Virtex-5

FPGA 还包含多种硬 IP 系统级模块,包括强大的 36Kb Block RAM/FIFO、第二代 25 x 18 DSP Slice、带有内置数控阻抗的

SelectIO™ 技术、ChipSync™ 源同步接口模块、系统监视器功能、带有集成 DCM(数字时钟管理器)和锁相环 (PLL) 时钟

发生器的增强型时钟管理模块以及高级配置选项。LXT 和 SXT 器件还包含针对增强型串行连接的电源优化高速串行收发器模

块、一个符合 PCI Express™ 的集成端点模块和三态以太网 MAC (媒体访问控制器)。这些功能使高级逻辑设计人员能够

在其基于 FPGA 的系统中体现最高档次的性能和功能。Virtex-5 FPGA 以最先进的 65nm 铜工艺技术为基础,是定制 A S I C

技术的可编程替代方案。大多数高级系统设计都需要 FPGA 的可编程能力。Virtex-5 FPGA 以前所未有的逻辑、DSP、软/

硬微处理器和连接功能提供最佳解决方案,以满足高性能逻辑设计人员、高性能 DSP 设计人员和高性能嵌入式系统设计人员

的需求。Virtex-5 LXT、SXT 和 FXT 平台具有先进的高速串行连接功能和链路 / 事务层功能。

Virtex-5 特性提要

• LX、LXT、SXT 和 FXT 四个平台

- Virtex-5 LX:高性能通用逻辑应用

- Virtex-5 LXT:具有高级串行连接功能的高性能逻辑

- Virtex-5 SXT:高性能信号处理应用

- Virtex-5 FXT:高性能嵌入式系统

• 跨平台兼容性

- LXT、SXT 和 FXT 器件在相同封装中的占用空间兼容

• 最先进的最佳利用率高性能 FPGA 架构

- 真 6 输入查找表 (LUT) 技术

- 双 5-LUT 选项

- 改进的布线减少了中间连线

- 64 位分布式 RAM 选项

- SRL32/ 双 SRL16 选项

• 强大的时钟管理模块 (CMT) 时钟控制

- 具有零延迟缓冲、频率综合和时钟相移功能的数字时钟管

理器模块

- 具有输入抖动滤波、零延迟缓冲、频率综合和相位匹配时

钟分频功能的 PLL 模块

• 36Kb Block RAM/FIFO

- 真双端口 RAM 模块

- 增强的可选可编程 FIFO 逻辑

- 可编程

· 高达 36 位的真正双端口宽度

· 高达 72 位的简单双端口宽度

- 内置可选纠错电路

- 可选择将每个模块作为两个独立的 18Kb 模块进行编程

• 65nm 铜 CMOS 工艺技术

• 1.0V 核电压

• 可选择标准或无铅的具有高度信号完整性的倒装芯片

封装

• 高性能并行 SelectIO 技术

- 1.2 到 3.3V I/O 运行

- 使用 ChipSync 技术的源同步接口连接

- 数控阻抗 (DCI) 有效终端

- 灵活的细粒度 I/O 分组

- 支持高速存储器接口

• 高级 DSP48E Slice

- 25x18 补数乘法运算

- 可选加法器、减法器和累加器

- 可选流水线功能

- 可选位宽逻辑功能

- 专用的级联连接

• 灵活的配置选项

- SPI 和并行 FLASH 接口

- 专用的回读重新配置逻辑,可支持多比特流

- 自动总线宽度检测功能

• 用于 PCI Express (LXT/SXT) 的集成端点模块

- 符合 PCI Express 基础规范 (PCI Express Base

Specification) 1.1

- 每模块支持 1 倍、2 倍、4 倍或 8 倍通道宽度

-与 RocketIO™ 收发器配合使用

• 三态 10/100/1000 Mb/s 以太网 MAC

(LXT/SXT)

- 可以将 RocketIO 收发器用作 PHY,也可以用多种软 MII

(媒体独立接口)方案将其连接到外部 PHY

• 100 Mb/s 到 3.2 Gb/s 的 RocketIO GTP 收发器

(LXT/SXT)

• 所有器件都有系统监视功能

- 片上 / 片外热特性监视

- 片上 / 片外电源监视

- 通过 JTAG 端口访问所有监视量

0

Virtex-5 系列概述

LX、LXT 和 SXT 平台

DS100 (v3.0) 2007 年 2 月 2 日

00

先期产品技术说明

R

Virtex-5 系列概述 LX、LXT 和 SXT 平台

DS100 (v3.0) 2007 年 2 月 2 日 www.xilinx.com/cn

先期产品技术说明 2

R

Virtex-5 逻辑架构

• 高达 50% 的速度提升

• 与 Virtex-4 器件相比,平均提升一到两个速度级别

• 可级联的 32 位变量移位寄存器或 64 位分布式存储器功

能

• 优异的布线架构,增强了对角线方向的布线支持,模块

与模块连接使用中间连线极少

• 多达 330,000 个逻辑单元,包括:

- 多达 207,360 个具有时钟使能的内部架构触发器

(XC5VLX330)

- 多达 207,360 个真 6 输入 LUT,总 LUT 位数大于

1300 万

- 两个双 5-LUT 模式输出提高了利用率

- 逻辑扩展多路复用器和 I/O 寄存器

550 MHz 时钟技术

• 多达六个时钟管理模块 (CMT)

- 每个 CMT 包含两个 DCM 和一个 PLL/PMCD - 时

钟发生器总数多达 18 个

- 灵活的 DCM 对 PLL 或 PLL 对 DCM 级联

- 精密时钟去歪斜和相移

- 灵活的频率综合

- 多种运行模式,便于性能权衡决策

- 提高了输入 / 输出频率上限

- 细粒度相移分辨率

- 输入抖动滤波

- 低功耗运行

- 相移范围大

- 相位匹配时钟分频器 (PMCD) 功能

• 可实现优化低抖动时钟和精确占空比的差分时钟树结构

• 32 个全局时钟网络

• 除了全局时钟,还有局部时钟、I/O 时钟和本地时钟

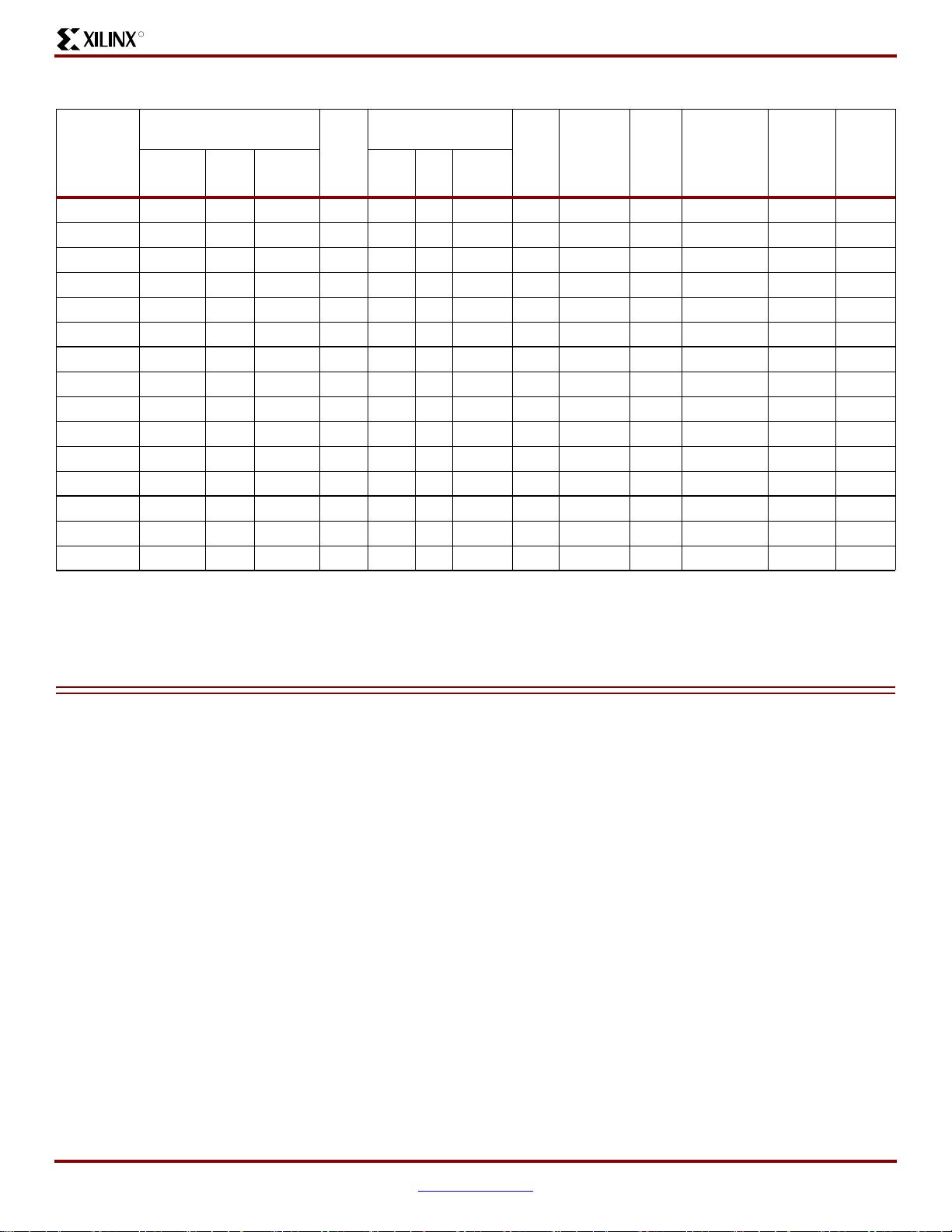

表 1:

Virtex-5 FPGA 系列成员

器件

可配置逻辑块

(

CLB)

DSP48E

Slice

(2)

Block RAM 模块

CMT

(4)

PCI Express

端点模块

以太网

MAC 模

块

RocketIO GTP

收发器

(5)

I/O 组

总数

最大

用户

I/O 数

(6)

阵列

(行 x 列)

Virtex- 5

Slice

(1)

最大

分布式

RAM (Kb)

18 Kb

(3)

36 Kb 最大 (Kb)

XC5VLX30

80 x 30 4,800 320 32 64 32 1,152 2 无 无 无 13 400

XC5VLX50

120 x 30 7,200 480 48 96 48 1,728 6 无 无 无 17 560

XC5VLX85

120 x 54 12,960 840 48 192 96 3,456 6 无 无 无 17 560

XC5VLX110

160 x 54 17,280 1,120 64 256 128 4,608 6 无 无 无 23 800

XC5VLX220

160 x 108 34,560 2,280 128 384 192 6,912 6 无 无 无 23 800

XC5VLX330

240 x 108 51,840 3,420 192 576 288 10,368 6 无 无 无 33 1,200

XC5VLX30T

80 x 30 4,800 320 32 72 36 1,296 2 1 4 8 12 360

XC5VLX50T

120 x 30 7,200 480 48 120 60 2,160 6 1 4 12 15 480

XC5VLX85T

120 x 54 12,960 840 48 216 108 3,888 6 1 4 12 15 480

XC5VLX110T

160 x 54 17,280 1,120 64 296 148 5,328 6 1 4 16 20 680

XC5VLX220T

160 x 108 34,560 2,280 128 424 212 7,632 6 1 4 16 20 680

XC5VLX330T

240 x 108 51,840 3,420 192 648 324 11,664 6 1 4 24 27 960

XC5VSX35T

80 x 34 5,440 520 192 168 84 3,024 2 1 4 8 12 360

XC5VSX50T

120 x 34 8,160 780 288 264 132 4,752 6 1 4 12 15 480

XC5VSX95T

160 x 46 14,720 1,520 640 488 244 8,784 6 1 4 16 19 640

注:

1. Virtex-5 Slice 的组织方式与前几代不同。每个 Virtex-5 Slice 包含四个 LUT 和四个触发器 (以前是两个 LUT 和两个触发器)。

2. 每个 DSP 48E 包含一个 25 x 18 位乘法器、一个加法器和一个累加器。

3. Virtex-5 Block RAM 的基本容量为 36 Kb。每个模块也可用作两个独立的 18Kb 模块。

4. 每个时钟管理模块 (CMT) 包含两个 DCM 和一个 PLL。

5. RocketIO GTP 收发器的设计运行速度为 100 Mb/s 到 3.2 Gb/s。

6. 此数字不包括 RocketIO 收发器。

Virtex-5 系列概述 LX、LXT 和 SXT 平台

DS100 (v3.0) 2007 年 2 月 2 日 www.xilinx.com/cn

先期产品技术说明 3

R

550 MHz 集成块存储器

• LXT 平台的集成模块存储器容量高达 11.6 Mb

• 带有可选双 18Kb 模式的 36Kb 模块

• 真双端口 RAM 单元

• 独立的端口宽度选择 (1 位宽到 72 位宽)

- 对于真双端口运行,每端口宽度可达 36 位宽

- 对于简单双端口运行 (一个读端口和一个写端口),

每端口宽度可达 72 位宽

- 9 位、18 位、36 位和 72 位宽度的存储器位数及奇偶

校验 / 边带存储器支持

- 从 32K x 1 到 512 x 72 的配置(8K x 4 到 512 x 72 用

于 FIFO 运行)

• 多采样率 FIFO 支持逻辑

- 具有完全可编程近满标志和近空标志的满标志和空标

志

• 同步 FIFO 支持,没有标志不确定的问题

• 用于提高性能的可选流水线级数

• 字节写功能

• 专用级联布线,无需 FPGA 布线即可形成 64K x 1 存储

器

• 满足高可靠性存储器要求的集成可选 ECC

• 针对 18 Kb (及以下)运行的特殊降功耗设计

550 MHz DSP48E Slice

• 25 x 18 补数乘法运算

• 用于增强性能的可选流水线级数

• 用于乘法累加 (MACC) 运算的可选 48 位累加器,可选

择将累加器级联为 96 位

• 用于复数乘法运算或乘加运算的集成加法器

• 可选按位逻辑运行模式

• 每 Slice 独立 C 寄存器

• 在一个 DSP 列中完全可级联,无需外部布线资源

SelectIO 技术

• 多达 1,200 个用户 I/O

• 广泛的 I/O 标准选择范围:从 1.2V 到 3.3V

• 极高的性能

- 高达 800 Mb/s 的 HSTL 和 SSTL (在所有单端 I/O

上)

- 高达 1.25 Gb/s LVDS (在所有差分 I/O 对上)

• 真差分片上终端

• 输入和输出 I/O 同边沿采集

• 广泛的存储器接口支持

65 nm 铜 CMOS 工艺

• 1.0V 核电压

• 12 层金属提供最强的布线功能,并可容纳硬 IP 植入

• 确实可减少静态功耗的三栅极氧化层技术

ChipSync 源同步接口逻辑

• 与 SelectIO 技术配合使用,简化源同步接口

• 所有 I/O 模块均内置逐比特去歪斜功能 (所有输入和输

出上的可变延迟线)

• 专用的 I/O 和区域时钟资源 (引脚和时钟树)

• 所有 I/O 均内置数据串行器 / 解串器逻辑,具有相应的时

钟分频器支持

• 速度高达 1.25 Gb/s 的网络 / 电信接口

数控阻抗 (DCI) 有效的 I/O 终端

• 可选串行或并行终端

• 温度和电压补偿

• 大幅度简化电路板布局

- 减少电阻器

- 在理想的位置设置终端,可以在信号源或信号终点

配置

• 支持 Platform Flash 配置、标准 SPI Flash 配置或标准

并行 NOR Flash 配置

• 专用的回读重新配置逻辑,可支持比特流

• 256 位 AES 比特流解密,可保护知识产权并防止复制设

计

• 改进的比特流检错 / 纠错功能

• 自动总线宽度检测功能

• 通过 ICAP 端口进行部分重配置

系统监视器

• 片上温度测量 (±4°C)

• 片上电源测量 (±1%)

• 易用性和自包含性

- 基本运行无需设计

- 所有片上传感器自行监视

- 片上传感器的用户可编程报警阀值

• 用户可访问的 10 位 200kSPS ADC

- 偏移和增益误差的自动校准

- DNL = ±0.9 LSB 最大

• 可支持多达 17 个外部模拟输入通道

- 输入范围为 0V 到 1V

- 监视外部传感器,如电压、温度

- 通用模拟输入

• 可以通过架构或 JTAG TAP 全面访问系统监视器

• 在 FPGA 配置之前和器件断电期间完全可运行 (仅通

过 JTAG TAP 访问)

先进的倒装芯片封装

• 确实可实现优异信号完整性的预制封装技术

- 尽量减少信号到返回之间的感应环路

- 最佳信号与 PWR/GND 比

• 将 SSO 感应噪声降低到 1/7

• 无铅封装与标准封装

剩余10页未读,继续阅读

资源评论

楚存达

- 粉丝: 0

- 资源: 8

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Win64OpenSSL-3-3-0.exe

- 课高分程设计-基于C++实现的民航飞行与地图简易管理系统-南京航空航天大学

- 航天器遥测数据故障检测系统python源码+文档说明+数据库(课程设计)

- 北京航空航天大学操作系统课设+ppt+实验报告

- 基于Vue+Echarts实现风力发电机中传感器的数据展示监控可视化系统+源代码+文档说明(高分课程设计)

- 基于单片机的风力发电机转速控制源码

- 基于C++实现的风力发电气动平衡监测系统+源代码+测量数据(高分课程设计)

- 毕业设计- 基于STM32F103C8T6 单片机,物联网技术的太阳能发电装置+源代码+文档说明+架构图+界面截图

- 基于 LSTM(长短期记忆)(即改进的循环神经网络)预测风力发电厂中风力涡轮机产生的功率+源代码+文档说明

- 基于stm32f103+空心杯电机+oled按键+运动算法

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功