没有合适的资源?快使用搜索试试~ 我知道了~

课程设计报告——用硬件描述语言设计浮点乘法器(原码一位乘法)

需积分: 48 18 下载量 133 浏览量

2015-06-01

19:24:16

上传

评论 3

收藏 2.36MB DOC 举报

温馨提示

试读

26页

完完整整的课程设计报告——用硬件描述语言设计浮点乘法器(原码一位乘法),仅去除了作者和指导老师名字

资源推荐

资源详情

资源评论

计算机科学与工程学院

课程设计报告

题目全称: 用硬件描述语言设计浮点乘法器(原码一位乘法 )

课程名称: 计算机组成原理 任课教师:

指导老师:

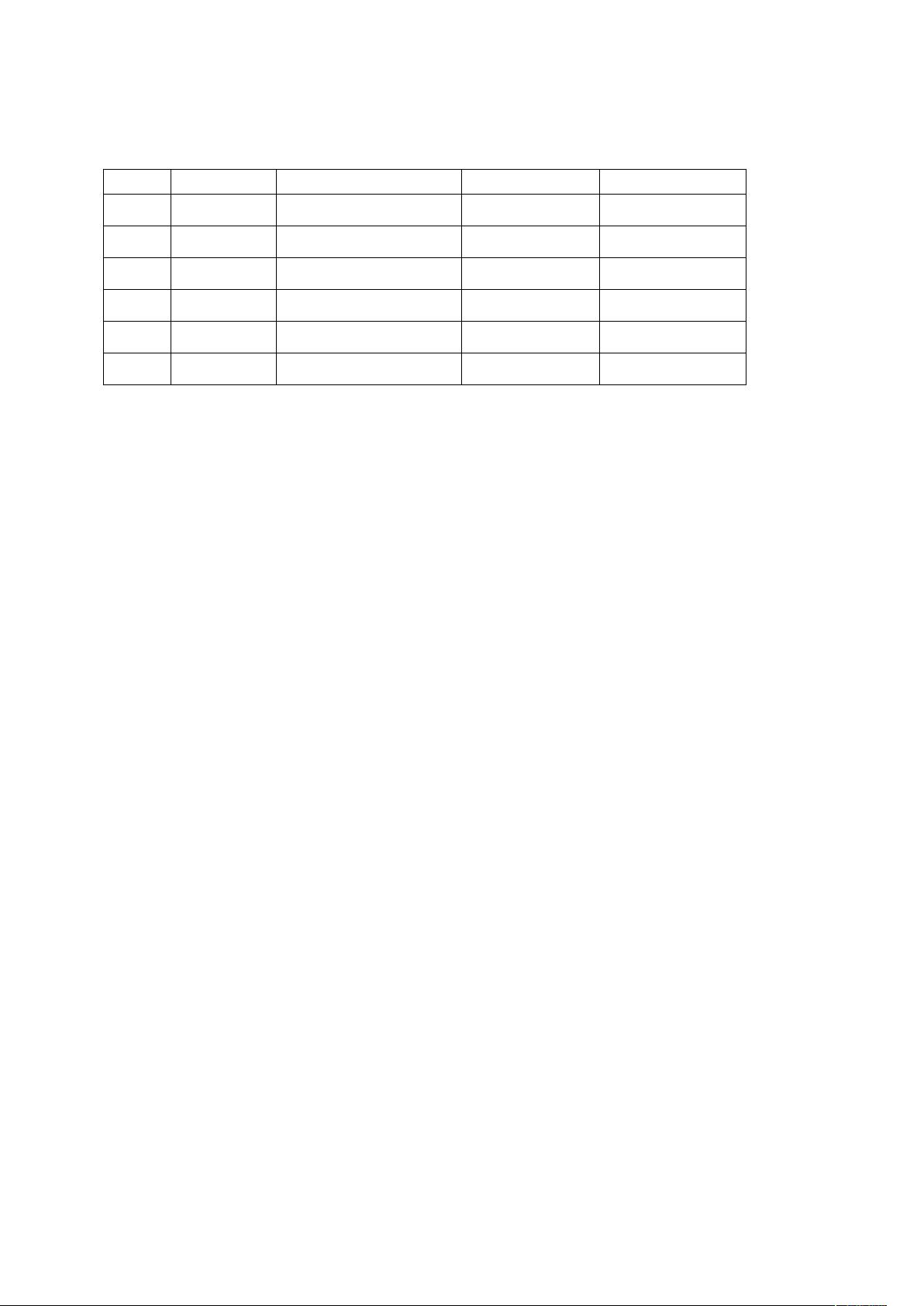

序号 学生姓名 学号 班号 任课教师 成绩

1

2

3

4

5

6

(注:学生姓名填写按学生对该课程设计的贡献及工作量由高到底排列,分数按排名依

次递减。序号排位为“1”的学生成绩最高,排位为“6”的学生成绩最低。)

指导老师评语:

工作态度

(10%)

课程设计的成

果(70%)

文档写作

(20%)

小组得分

(100%)

小组成员的分工及任务完成情况

1

签字:

序号 学生姓名 任务分工 完成情况 学生签名

1

2

3

4

5

6

2

目录

第一章 序章...................................................................................................................................................4

1.1 乘法器概述......................................................................................................................................4

1.2 课题概述..........................................................................................................................................5

第二章 课程设计的需求分析.......................................................................................................................6

2.1 环境需求..........................................................................................................................................6

2.2 功能需求..........................................................................................................................................6

2.3 性能需求..........................................................................................................................................6

第三章 总体设计...........................................................................................................................................7

3.1 原理分析..........................................................................................................................................7

第四章 乘法器的实现.................................................................................................................................13

4.1 开发环境介绍................................................................................................................................13

4.2 主要功能模块的实现....................................................................................................................13

第五章 测试及成果展示.............................................................................................................................20

5.1 测试环境........................................................................................................................................20

5.2 测试用例和结果............................................................................................................................20

5.3 成果展示........................................................................................................................................21

第六章 总结与展望.....................................................................................................................................25

参考文献......................................................................................................................................................26

III

第一章 序章

1.1 乘法器概述

作用

乘法器不仅作为乘法、除法、乘方和开方等模拟运算的主要基本单元,而且还广泛用于电子通信系统

作为调制、解调、混频、鉴相和自动增益控制;另外还可用于滤波、波形形成和频率控制等场合,因

此是一种用途广泛的功能电路。

一个理想的通用乘法器,不应当对任何一个输入信号的极性加以限制,也就是说,应当具有能完成四

个象限的运算功能的电路。

类型

模拟乘法器

模拟乘法器是对两个模拟信号(电压或电流)实现相乘功能的的有源非线性器件。主要功能是实现两

个互不相关信号相乘,即输出信号与两输入信号相乘积成正比。它有两个输入端口,即X和Y输入端

口。

乘法器两个输入信号的极性不同,其输出信号的极性也不同。如果用XY坐标平面表示,则乘法器有

四个可能的工作区,即四个工作象限,如图。

若信号均限定为某一极性的电压时才能正常工作,该乘法器称为单象限乘法器;若信号中一个能适应

正、负两种极性电压,而另一个只能适应单极性电压,则为二象限乘法器;若两个输入信号能适应四

种极性组合,称为四象限乘法器。

集成模拟乘法器的常见产品有BG314、F1595、F1596、MC1495、MC1496、LM1595、LM1596等。

硬件乘法器

硬件乘法器,其基础就是加法器结构,它已经是现代计算机中必不可少的一部分。乘法器的模型就是

基于“移位和相加”的算法。在该算法中,乘法器中每一个比特位都会产生一个局部乘积。第一个局部

乘积由乘法器的LSB产生,第二个乘积由乘法器的第二位产生,以此类推。如果相应的乘数比特位是

1,那么局部乘积就是被乘数的值,如果相应的乘数比特位是0,那么局部乘积全为0。每次局部乘积

都向左移动一位。

乘法器可以用更普遍的方式来表示。每个输入,局部乘积数,以及结果都被赋予了一个逻辑名称(如

A1、A2、B1、B2),而这些名称在电路原理图中就作为了信号名称。在原理图的乘法例子中比较信

号名称,就可以找到乘法电路的行为特性。

在乘法器电路中,乘数中的每一位都要和被乘数的每一位相与,并产生其相应的乘积位。这些局部乘

积要馈入到全加器的阵列中(合适的时候也可以用半加器),同时加法器向左移位并表示出乘法结果

最后得到的乘积项在CLA电路中相加。注意,某些全加器电路会将信号带入到进位输入端(用于替代

邻近位的进位)。这就是一种全加器电路的应用;全加器将其输入端的任何三个比特相加。

随着乘数和被乘数位数的增加,乘法器电路中的加法器位树也要相应的增加。通过研究CLA电路的特

性,也可以在乘法器中开发出更快的加法阵列。

4

1.2 课题概述

本课题的目的是掌握原码一位乘法的计算原理和分步乘法的过程,以及各个实现的模块

的工作原理及方式。同时通过实现乘法器的也为更复杂的乘法器打好理论和实践的基础

以便于理解和实现原码两位乘法器和更多位的乘法器。同时更加深了模块化的设计思想

由简到繁,逐步细化每个功能模块。此外,还为了更好地学会使用Verilog语言,熟悉了

语法、设计过程、调试方法,以及软硬件工作的配合。

5

剩余25页未读,继续阅读

资源评论

koala060528

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功