Enhanced Host Controller Interface Specification for

Universal Serial Bus

Date:

March 12, 2002

Revision:

1.0

EHCI Revision 1.0 3/12/2002

USB 2.0

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY

WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR ANY PARTICULAR

PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR

SAMPLE. Information in this specification is provided in connection with Intel products. No license, express

or implied, by estoppel or otherwise, to any intellectual property rights is granted herein, except that a license

is hereby granted to copy and reproduce this specification for internal use only.

Contact Intel for information on further licensing agreements and requirements.

Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to use of

information in this specification. Except as provided in Intel’s Terms and Conditions of Sale for such

products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating

to sale and/or use of Intel products including liability or warranties relating to fitness for a particular

purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel

products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to documents, specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved"

or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for

conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest documents and/or specifications,

and before placing any product order.

Copies of documents which have an ordering number and are referenced in this specification, or other Intel

literature, may be obtained from:

Intel Corporation

http://www.intel.com

or, call 1-800-548-4725

Copyright © Intel Corporation 1999 – 2001

* Third-party brands and names are the property of their respective owners.

EHCI Revision 1.0 3/12/2002

USB 2.0

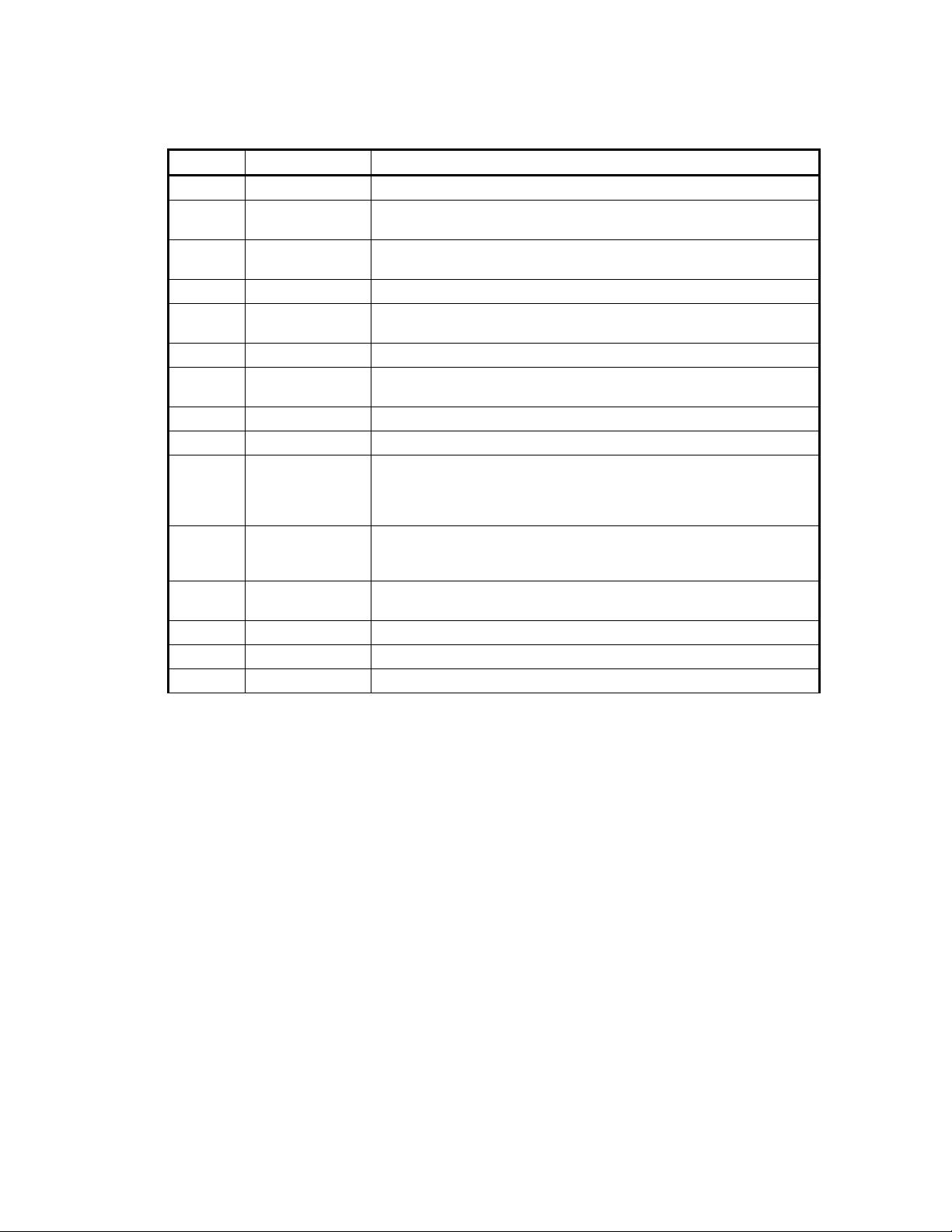

Revision History

Revision Issue Date Comments

0.8a 7/20/1999 Initial Revision

0.8b 8/10/1999 Added information in data structures to support split transactions,

etc. Started adding information into operational model (Chapter 4).

0.9 rc1 12/21/1999 Significant additions to complete definition for register space, data

structures and operational model.

0.9 rc2 1/3/2000 Updated based on 0.9rc1 feedback.

0.9 rc5 1/12/2000 Updated based on 0.9 rc2 feedback. Internal, incremental revisions

account rcX jump.

0.9 1/13/2000 Editorial changes from 0.9 rc5.

0.91 7/6/2000 Update for yellow cover release. Also includes additions for debug

port.

0.95 rc1 9/26/2000 Editorial updates. Deleted Chapter 5, Legacy Keyboard.

0.95 11/10/2000 Final editorial updates.

0.96 rc1 4/23/2001 Editorial clarifications; Fix for erratum on handling CErr during

Interrupt split transactions and new features for managing frame-

wrap FS/LS interrupt, Asynchronous Park-mode, FS/LS

Rebalancing and new EHCI ownership semaphores.

0.96.rc2 5/30/2001 Fixed numerous typos, relaxed requirements on park mode, added

CErr handling for FS/LS Setup transactions and numerous other

clarifications.

0.96.rc3 6/12/2001 Added requirement to handling of full-speed isochronous-IN data

streams (for compatibility).

0.96 6/20/2001 Final editorial edits, pagination, etc.

1.0 rc1 1/31/2002 Editorial changes accumulated from industry feedback.

1.0 3/13/2002 Editorial changes accumulated during Licensee Review Period.

NOTE TO SOFTWARE DEVELOPERS:

Revisions of the EHCI specification have introduced new features in the programming interface. Software

must not attempt to use features defined in recent revisions of the specification on host controllers designed

to older revisions. A summary of new features, per revision is provided below.

Revision Software-visible New Feature

• Frame Span Traversal Nodes (FSTN), see Section 3.7.

• Rebalance Lockout (I-Bit), see Sections 3.6, 4.12.2.5

• Asynchronous Park Mode, see Sections 2.2.4, 2.3.1, and 4.10.3.2.

• EHCI Extended Capabilities, see Section 5.

0.96

• Legacy Support, see Section 5.1

EHCI Revision 1.0 3/12/2002

USB 2.0

Significant Contributors:

John S. Howard Intel Corporation Nobuo Furuya NEC

Darren Abramson Intel Corporation James E. Guziak Lucent

Michael N. Derr Intel Corporation Brian Leete Intel Corporation

John Garney Intel Corporation Brad Hosler Intel Corporation

Karthi Vadivelu Intel Corporation Chris Robinson Microsoft

Ken Stufflebeam Compaq

Please send comments via electronic mail to: ehcisupport@intel.com